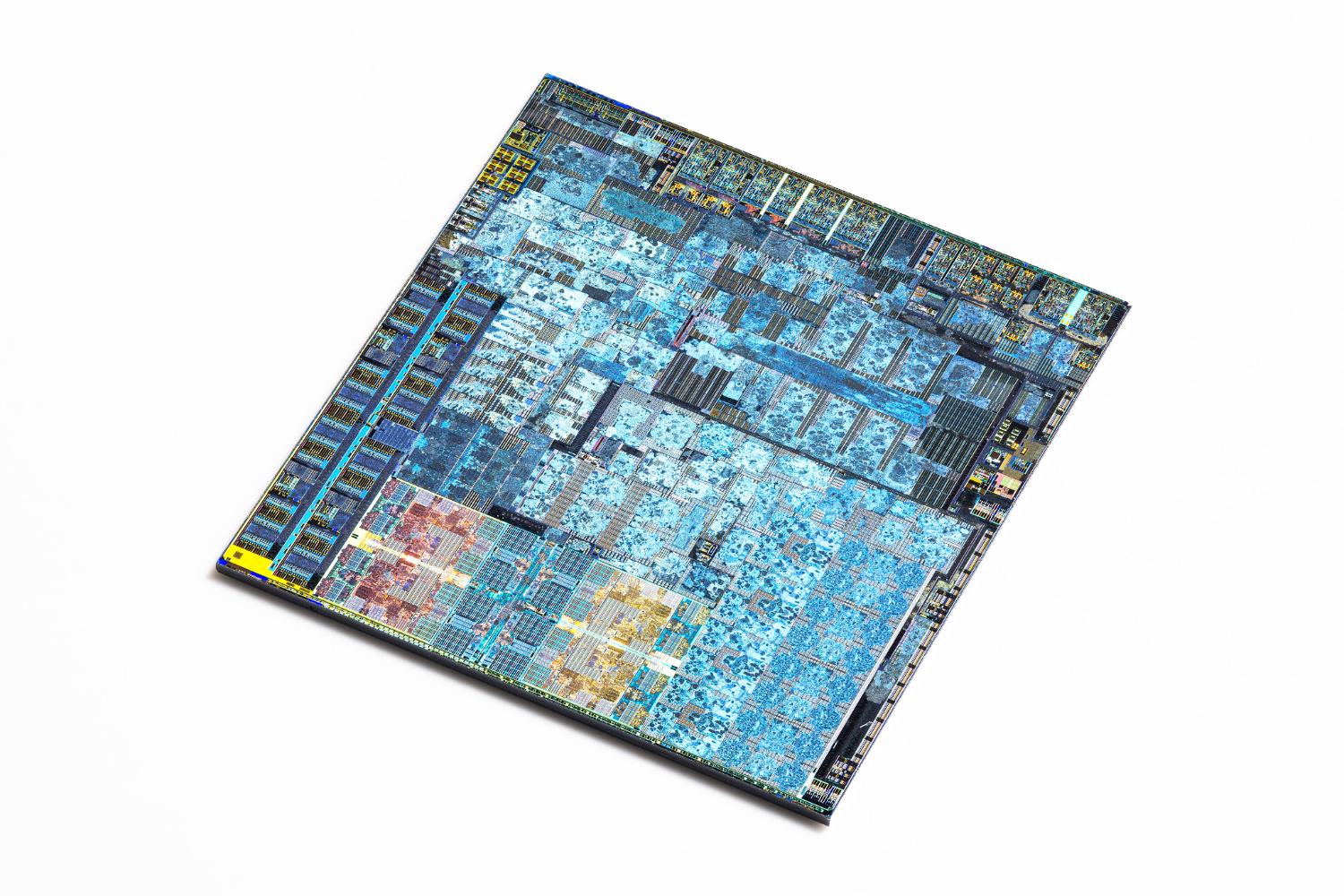

Los chips de 2 nm están a punto de convertirse en la nueva referencia de la industria de los semiconductores, pero no llegan en un contexto sencillo. Litografías cada vez más pequeñas, la explosión de la inteligencia artificial y la demanda brutal de centros de datos han llevado a fabricantes como TSMC, Samsung, Intel y AMD o Fujitsu a exprimir al límite sus capacidades técnicas y económicas.

Cuando se habla de 2 nanómetros en CPUs y SoC muchos usuarios piensan que se trata simplemente de un número menor que implica más potencia, pero la realidad es bastante más compleja. Los nm ya no describen de forma directa el tamaño físico de las puertas lógicas o la distancia entre transistores, sino que funcionan como una etiqueta comercial para agrupar generaciones de proceso con mayor densidad, mejor rendimiento y menor consumo.

Qué significa realmente fabricar chips de 2 nm

El llamado nodo de 2 nm es el siguiente paso después de los 3 nm en la hoja de ruta de la fabricación de semiconductores tipo MOSFET. Sin embargo, ese “2 nm” o los “20 angstroms” de los que habla Intel no se corresponden con ninguna dimensión concreta del transistor, como el gate length o el metal pitch. Según las proyecciones de la IEEE para el rango de nodo 2,1 nm, se espera un pitch de puerta de unos 45 nm y un pitch metálico mínimo en torno a los 20 nm.

En la práctica, 2 nm se utiliza como etiqueta de marketing para describir una nueva generación de procesos que incrementan la densidad de transistores, aumentan la velocidad y recortan el consumo energético respecto a los 3 nm. Esta denominación libera a los fabricantes de atarse a un valor geométrico fijo y les permite competir en términos de rendimiento global del nodo, aunque complique mucho que los usuarios comparen directamente TSMC, Samsung e Intel.

La transición a 2 nm implica, además, un cambio de arquitectura de transistores. Después de años refinando los FinFET, el sector ha virado hacia diseños gate-all-around FET (GAAFET). Aquí entran en juego tecnologías como los nanosheets horizontales (Samsung MBCFET, Intel Nanoribbon), nanocables verticales, CFET con transistores apilados, variantes como VFET, NC-FET con materiales exóticos, y futuros CFET con canales de materiales 2D como WS2 o grafeno.

Institutos como IMEC prevén una cadena de innovaciones para poder seguir escalando más allá de los 2 nm: adopción masiva de EUV de alta apertura numérica (0,55), interconexiones con nuevos metales como el rutenio, reducción drástica de la altura de celda estándar, distribución de potencia por la cara trasera de la oblea, air gaps en el dieléctrico y avances de empaquetado 2,5D y 3D con chiplets cada vez más estrechamente integrados.

Todo esto hace que el nodo de 2 nm no sea un “simple” die shrink sino un conjunto de cambios profundos en litografía, materiales, diseño de transistores y empaquetado que afecta tanto al rendimiento bruto como al rendimiento por vatio y a la fiabilidad de los chips.

Qué mejoras de rendimiento y eficiencia se esperan de los 2 nm

Los objetivos de los nodos de 2 nm son claros: más rendimiento y mejor eficiencia. Pasar de 3 nm a 2 nm debería suponer, de media, un aumento del rendimiento de entre un 10 % y un 15 %, una reducción del consumo eléctrico en el rango del 20 % al 30 % y, aproximadamente, una mejora del 15 % en densidad de transistores, según cifras que manejan arquitectos de software y diseño EDA como los de Synopsys.

En el terreno de escritorio, el usuario asocia estos avances a más FPS y mayor fluidez al mover aplicaciones pesadas, juegos o tareas creativas. Aunque el consumo y las temperaturas importan, ya se han visto ejemplos de procesos “no tan extremos” como los 4 nm de Ryzen 9000 ofreciendo CPUs bastante frías y eficientes. Esto pone el listón muy alto a los 2 nm, que tienen que justificar un salto de coste enorme.

TSMC, con su plataforma N2, habla de cifras en la misma línea: entre un 10 y un 15 % más de rendimiento a igualdad de consumo, o entre un 20 y un 30 % menos de energía a igualdad de rendimiento, además de más de un 20 % de incremento en densidad frente a N3E. En demostraciones internas se ha visto, por ejemplo, un núcleo ARM Cortex-A715 fabricado en N2 que logra ser en torno a un 16 % más rápido al mismo consumo, o ahorrar más de un 37 % de potencia manteniendo el rendimiento.

Para el usuario final, eso se traduce en dispositivos más pequeños o con más autonomía, portátiles más delgados con mejor batería, smartphones que ejecutan modelos de IA localmente con menos gasto energético y servidores capaces de mover cargas de IA masivas con un coste operativo ligeramente más contenido.

El problema es que más frecuencia y más transistores por mm² implican más calor. La relación es sencilla: más rendimiento implica aumentar la frecuencia y la cantidad de lógicas activas, lo que eleva la disipación térmica. Si las temperaturas se disparan, entran en juego mecanismos de throttling y se pierde parte del beneficio de la nueva litografía. De ahí que buena parte de la innovación se esté centrando tanto en la parte térmica como en la de empaquetado y distribución de potencia.

Retos térmicos, FinFET, GAAFET y la física que no perdona

Desde la llegada de FinFET y la reducción agresiva de nodos han ido apareciendo problemas térmicos cada vez más complicados de manejar, especialmente en dispositivos móviles y en servidores, donde la densidad de potencia es brutal. En sobremesa siempre cabe la solución obvia: un disipador colosal, más ventilación o incluso refrigeración líquida. En un smartphone, un reloj inteligente o un blade de un datacenter esa opción no existe.

Por eso los fabricantes llevan años investigando nuevas estructuras de transistor. Samsung fue de las primeras en apostar fuerte por GAAFET (su MBCFET), experimentando también con materiales como el molibdeno o compuestos alternativos para el canal. IBM, por su parte, demostró en 2021 un chip experimental de 2 nm con transistores GAAFET de nanosheets de silicio y longitudes de puerta de unos 12 nm, marcando un hito en el laboratorio.

El salto de FinFET a GAAFET permite un control mucho más fino del canal, lo que reduce fugas, mejora el comportamiento a bajos voltajes y ayuda a exprimir más rendimiento por vatio. Además, se abren posibilidades como los CFET (pFET y nFET apilados verticalmente) que prometen aún más densidad en el futuro, e incluso diseños verticales tipo VTFET ya demostrados a escalas sub-45 nm de pitch de puerta.

Aun así, la termodinámica manda. Cada vatio que entra en el chip tiene que salir en forma de calor, y en nodos tan pequeños la superficie efectiva para disipar no crece al mismo ritmo que el número de transistores. De ahí que la industria se centre también en técnicas como la distribución de potencia por la parte trasera (backside power), metalizaciones más eficientes y empaquetados 2,5D/3D pensados para mejorar la evacuación térmica.

Los dispositivos móviles y el HPC son los que más sufren esta tensión: necesitan mucha capacidad de cómputo sostenida y, al mismo tiempo, límites muy estrictos de consumo y temperatura. Los 2 nm pueden ayudar, pero no solucionan mágicamente el problema del calor; obligan a un equilibrio continuo entre densidad, frecuencia, voltaje y refrigeración.

TSMC, Samsung, Intel y la carrera industrial por los 2 nm

TSMC es actualmente el actor dominante en la fabricación de chips avanzados, con una cuota cercana al 60 % del mercado de foundries y un historial muy sólido en nodos como 7 nm, 5 nm y 3 nm. La compañía empezó a investigar seriamente los 2 nm en torno a 2019, con la idea clara de pasar de FinFET a GAAFET, y ha recibido apoyo gubernamental taiwanés para construir fábricas específicas como la Fab 20 y la Fab 22 dedicadas a N2.

Según su hoja de ruta, TSMC inició la fase de riesgo de N2 en 2024, con la entrada en producción inicial prevista para la segunda mitad de 2025. De hecho, se ha confirmado el arranque de la producción en serie de chips de 2 nm en Fab 22 en Kaohsiung a finales de 2025, convirtiendo este nodo en el más avanzado disponible en términos de densidad y eficiencia energética para clientes como MediaTek, Apple, NVIDIA, AMD o Qualcomm.

Samsung, por su lado, no llega en su mejor momento financiero. Sus ingresos en semiconductores cayeron más de un 37 % en 2023 respecto a 2022 y se ha visto forzada a revisar planes de expansión y ajustar plantilla. Aun así, lleva años preparando su proceso de 2 nm, conocido como 2GAP, basado en MBCFET. La compañía ha reafirmado su intención de entrar en producción en masa a partir de 2025, incrementando el número de nanosheets frente a 3 nm y apostando por metalizaciones como el “single-grain metal” para reducir resistencias.

Intel juega una partida distinta, intentando reconvertirse desde una IDM tradicional a un modelo también de foundry para terceros. Su plan original contemplaba un nodo Intel 20A (equivalente comercial a 2 nm) para 2024 y un 18A para 2025, con tecnologías clave como RibbonFET (su versión de GAAFET) y PowerVia (alimentación por la cara trasera). Sin embargo, la empresa decidió cancelar la rampa de 20A para centrarse en 18A, ahorrando más de 500 millones de dólares y reutilizando los avances de 20A para acelerar el desarrollo de 18A.

Este 18A, que Intel posiciona aproximadamente como un proceso de 1,8 nm, ya ha alcanzado madurez suficiente para producción a gran escala en 2025 y se ha reportado que ofrece en torno a un 15 % más de eficiencia energética y un 30 % más de densidad frente a Intel 3. Procesadores como Panther Lake y Clearwater Forest para el mercado Xeon, así como futuras familias de consumo, se apoyarán en él para competir directamente con N2 de TSMC.

Mientras tanto, Europa y Japón también quieren su trozo del pastel. Un bloque de 17 países de la Unión Europea ha comprometido hasta 145.000 millones de euros para reforzar toda la cadena de valor de semiconductores, con la vista puesta en nodos tan avanzados como 2 nm. En Japón, el consorcio Rapidus, con apoyo estatal, acuerdos con IMEC e IBM, y planes de prueba de producción en 2 nm en su planta IIM-1, pretende devolver al país a la primera línea de la fabricación avanzada.

Cuello de botella: CoWoS-L, empaquetado avanzado y escasez

El gran problema de la transición a 2 nm no es solo fabricar buenas obleas, sino empaquetar los chips resultantes en configuraciones cada vez más complejas. Muchas de las soluciones más punteras para IA y HPC ya no son “chips monolíticos” clásicos, sino sistemas de varios die apilados o interconectados mediante interposers de altísima densidad, como la tecnología CoWoS-L de TSMC.

CoWoS-L permite colocar múltiples chips sobre un interposer con un cableado extremadamente denso, perfecto para unir dies de cómputo con pilas de memoria HBM o bloques de caché 3D. Pero también introduce retos enormes, como la dilatación térmica diferencial entre los distintos materiales, que puede generar deformaciones, microfisuras o fallos en las interconexiones a medida que el chip se calienta y enfría en operación.

Buena parte de la capacidad de CoWoS-L de TSMC está comprometida. Se estima que NVIDIA habría acaparado alrededor del 70 % de la producción para sus GPUs y aceleradores de IA de nueva generación, lo que genera una especie de cuello de botella para otros clientes que también necesitan empaquetado avanzado: AMD con sus procesadores con 3D V-Cache, futuros Intel bLLC para competir con los X3D de AMD en gama doméstica, y grandes CPUs EPYC o Xeon con enormes cantidades de caché integrada.

Esta saturación ya ha afectado a productos clave. Los chips basados en arquitectura Blackwell de NVIDIA han sufrido retrasos múltiples, en parte por problemas de rendimiento y capacidad de CoWoS-L. Al mismo tiempo, TSMC tiene que equilibrar las líneas dedicadas a 3 nm y 5 nm, que aún mueven volúmenes muy altos, con las inversiones multimillonarias necesarias para escalar 2 nm, tanto en front-end (fab) como en back-end (empaquetado).

Todo esto significa que no vamos a ver una avalancha de chips en 2 nm de golpe. Muchas compañías preferirán seguir fabricando en 3, 4 o 5 nm para la mayoría de sus productos, reservando los 2 nm solo para gamas muy concretas donde el diferencial de rendimiento o eficiencia compense el coste astronómico de las obleas y el empaquetado avanzado.

De los 14 nm a los 2 nm: un salto menos “fluido” de lo esperado

Si miramos atrás, la transición de 14 nm a 7 nm y 5 nm pareció relativamente rápida, al menos en el ecosistema TSMC. Sus nodos de 7 y 5 nm se han mostrado maduros y fiables, con unos rendimientos por oblea muy altos y sin grandes escándalos técnicos. Intel, en cambio, vivió una odisea al pasar de 10 nm a 7 nm, con retrasos, re-diseños y cambios de estrategia que lastraron su competitividad durante años.

La diferencia ahora es que el avance de litografía se ha combinado con una demanda brutal procedente de los centros de datos y la IA, además de una expansión histórica en dispositivos móviles. TSMC ya lo tenía complicado para responder a todos los pedidos en 5 y 3 nm, como para encima volcar recursos masivos en nuevas fábricas, EUV de alta NA y desarrollo de N2 sin resentir el suministro actual.

El paso de 7 a 6 nm o de 5 a 4 nm fue relativamente modesto en cuanto a ganancias de rendimiento y eficiencia, y se hizo más para optimizar costes y reutilizar IP que como salto revolucionario. El de 5 a 3 nm sí ha sido mucho más notable, y ahí es donde compañías como AMD, NVIDIA, Qualcomm, Samsung o la propia Apple han visto beneficios reales para sus SoC de gama alta.

Con los 3 nm ya sobre la mesa, el coste por oblea se disparó alrededor de un 50 % frente a 5 nm, y con 2 nm la factura vuelve a multiplicarse. No es trivial justificar un nodo que puede, en la práctica, llegar a costar el doble por oblea cuando muchos productos van “sobrados” con 3 o 4 nm. De ahí que los 2 nm se vayan a concentrar en chips de muy alto valor añadido, sobre todo en datacenters, supercomputación e IA.

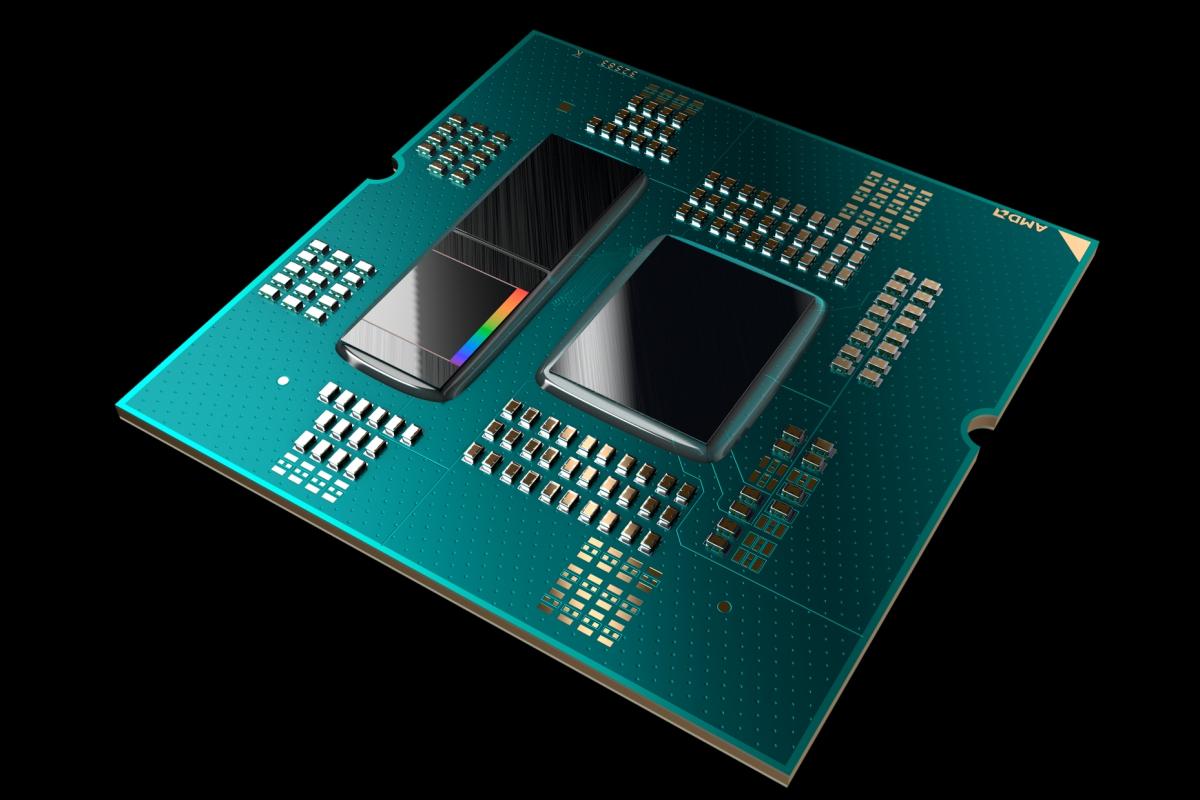

Por si fuera poco, la densidad creciente obliga a rediseñar cómo se distribuyen las funciones dentro de un procesador. Intel ya ha optado por separar tiles con distintas litografías dentro del mismo paquete para equilibrar coste y rendimiento, mientras que AMD combina chiplets de núcleos en un nodo avanzado con un die de I/O en un proceso más maduro y barato. Este enfoque heterogéneo será cada vez más habitual y, a nivel doméstico, es más probable ver CPUs con uno o varios bloques en 2 nm que un chip completamente monolítico en 2 nm.

Chips concretos de 2 nm: de Fujitsu-MONAKA a AMD Venice y Exynos 2600

Más allá de los powerpoints, ya hay proyectos concretos en 2 nm dando que hablar. Uno de los más llamativos es el procesador Fujitsu-MONAKA, desarrollado por Fujitsu en colaboración con Broadcom y TSMC. Hablamos de un SoC con 144 núcleos pensado para la próxima generación de supercomputadoras japonesas, en concreto para la sucesora de Fugaku, conocida como FugakuNEXT y liderada por el instituto RIKEN.

MONAKA utiliza un empaquetado avanzado 3.5D (XDSiP) y se centra en maximizar la eficiencia energética en entornos de High Performance Computing (HPC) y grandes cargas de IA. Incorpora un subsistema de memoria con doce canales DDR5, que combinado con soporte para PCIe 6.0 y CXL 3.0 lo convierte en una bestia de ancho de banda, ideal para entrenar modelos de IA colosales o ejecutar simulaciones científicas extremadamente complejas.

Este diseño no compite directamente con CPUs domésticas como Ryzen o Core, sino con aceleradores de gama profesional como AMD Instinct, NVIDIA Grace/Grace Hopper o las soluciones Xeon y Gaudi de Intel. Su enfoque está en datacenters y supercomputación, no en PC o móviles, pero demuestra que los 2 nm ya no son solo una promesa, sino una realidad física que se está fabricando.

En el mundo x86, AMD ha anunciado su primer silicio en 2 nm: un CCD (Core Complex Die) para sus procesadores EPYC de sexta generación, con nombre en clave “Venice”, fabricados en N2 de TSMC. Estos chips, basados en la microarquitectura Zen 6, están previstos para llegar alrededor de 2026 y se inscriben de lleno en la batalla por el mercado de servidores y computación en la nube.

Las cifras que maneja TSMC para este proceso aplicado a EPYC Venice hablan de reducciones de consumo del 24 % al 35 % o incrementos del 15 % en rendimiento a voltaje constante respecto a los 3 nm de clase N3, además de una densidad de transistores aproximadamente 1,15 veces mayor. El primer CCD ha pasado ya pruebas funcionales básicas (tape-out y bring-up), un paso clave para validar el nodo en un diseño complejo real.

En el terreno móvil, Samsung ha presentado a bombo y platillo su Exynos 2600 como el primer SoC de 2 nm orientado a smartphones. La compañía presume de una mejora de más del 100 % en capacidad de IA y de un rendimiento gráfico que prácticamente se duplica frente a la generación previa, posicionando este chip para competir de tú a tú con los futuros Apple A20 para iPhone y con soluciones de Qualcomm y MediaTek de gama superior.

Aunque muchos de estos chips aún están en fase de pruebas o ramp-up, representan claramente la dirección de la industria: 2 nm para IA, HPC, servidores y gama ultra premium de móviles, mientras la mayoría del mercado seguirá moviéndose cómodamente en 3, 4 y 5 nm durante bastante tiempo.

Qué esperar en CPUs domésticas y qué nodos veremos en la práctica

En ordenadores domésticos, la adopción de 2 nm va a ser más gradual. Hoy en día, la mayoría de CPUs de sobremesa y portátiles de gama alta se fabrican en nodos entre 4 y 5 nm (Ryzen 7000/8000/9000, por ejemplo) o equivalentes en la nomenclatura de Intel. Estos procesos ya ofrecen un rendimiento y eficiencia excelentes, hasta el punto de que para la mayoría de usuarios el cuello de botella no es la litografía.

El gran motor de cambio en PC es la integración de aceleradores de IA como NPUs dedicadas, algo que ya estamos viendo con las plataformas de “PC con IA” tanto de Intel como de AMD y otros fabricantes. A medida que estos bloques se vuelvan más complejos y potentes, los 2 nm permitirán meter más capacidades de IA en el mismo espacio y con menos consumo, pero sigue siendo una cuestión de coste-beneficio.

Lo más probable es ver diseños heterogéneos en los que solo parte del chip esté en 2 nm: tiles de núcleos de alto rendimiento o bloques de IA en el nodo más avanzado, acompañados por chips de E/S, gráficos integrados o comunicación en nodos más maduros. Es el enfoque que ya está usando Intel con sus diseños multi-tile y que AMD domina con sus chiplets de núcleos + die de I/O.

En móviles, tablets y wearables, el argumento de la autonomía es clave. Un SoC de 2 nm que mantenga el mismo rendimiento que uno de 3 nm puede ofrecer un recorte importante de consumo que se traduce en más horas de pantalla. Pero, de nuevo, solo los modelos de gama alta y ultra premium podrán asumir el coste de un nodo tan caro, mientras que la gama media y baja seguirán varios pasos por detrás.

A largo plazo, también veremos 2 nm colándose en dispositivos de red, IoT avanzado y edge computing, especialmente donde haya cargas de IA en el extremo de la red que requieran mucha potencia de cómputo en espacios muy reducidos. Pero esto dependerá de que los rendimientos por oblea alcancen niveles razonables (por encima del 70 %), algo que hoy sigue siendo un desafío importante para todas las foundries.

La consecuencia práctica para el usuario de a pie es que oirá hablar mucho de 2 nm en presentaciones de producto y notas de prensa, pero tardará más en notar un salto tan revolucionario como el que supuso, en su día, el paso de arquitecturas muy antiguas a las actuales. El avance seguirá siendo real, pero más incremental y concentrado en segmentos muy concretos del mercado.

En definitiva, los chips de 2 nm representan una nueva vuelta de tuerca en la miniaturización de CPUs y SoC, con mejoras tangibles en rendimiento por vatio, densidad y capacidades de IA, aunque llegan acompañados de enormes retos técnicos, térmicos y económicos. La apuesta de TSMC, Samsung, Intel, AMD, Fujitsu y otros actores por esta litografía marcará la próxima década de la computación, pero durante bastante tiempo convivirá con nodos de 3, 4 y 5 nm que seguirán siendo el caballo de batalla de la industria.

Redactor apasionado del mundo de los bytes y la tecnología en general. Me encanta compartir mis conocimientos a través de la escritura, y eso es lo que haré en este blog, mostrarte todo lo más interesante sobre gadgets, software, hardware, tendencias tecnológicas, y más. Mi objetivo es ayudarte a navegar por el mundo digital de forma sencilla y entretenida.