- tRFC, tFAW, tRRD, tRRDL y tSTAG controlan procesos internos de la DRAM y afectan sobre todo a la estabilidad.

- Muchos subtimings tienen relaciones entre sí; forzarlos demasiado puede reducir el rendimiento o causar errores.

- Los perfiles XMP suelen ofrecer un equilibrio muy sólido entre seguridad y velocidad para uso real.

- Ajustar subtimings solo aporta mejoras marginales frente a optimizar frecuencia, timings principales y voltaje.

Cuando empiezas a trastear con la RAM, lo primero que miras son los tiempos principales: CL, tRCD, tRP y tRAS. Pero en cuanto te metes un poco más a fondo, aparecen siglas como tRFC, tFAW, tRRD, tRRDL y tSTAG que suenan a chino y que casi nunca se explican bien. Muchos usuarios ven que cambian estos valores al actualizar los módulos o activar un perfil XMP y se preguntan si realmente importan en el día a día, sobre todo para jugar o para tareas de productividad.

La realidad es que estas temporizaciones son parámetros internos que gobiernan cómo trabaja físicamente la memoria. No siempre se traducen en más FPS o más puntos en un benchmark, pero sí marcan la diferencia entre un sistema estable y uno que se cuelga al mínimo despiste. Además, afinarlos mal puede provocar el efecto contrario al deseado: menos rendimiento pese a tener valores “más agresivos”. Vamos a ver por qué pasa esto y qué pinta tiene cada timing.

Qué son tRFC, tFAW, tRRD, tRRDL y tSTAG en la RAM

En las especificaciones de la RAM verás que, además de los cuatro tiempos principales, hay una larga lista de subtimings. Entre ellos destacan tRFC, tFAW, tRRD, tRRDL y tSTAG, que controlan operaciones internas críticas de los chips DRAM. No gestionan directamente la latencia entre la CPU y la memoria, sino los tiempos de refresco, activación entre bancos y ciertas limitaciones de seguridad para evitar que los chips se saturen.

Muchos fabricantes de módulos, como G.SKILL, Crucial o Patriot, programan estos subtimings en los perfiles XMP o DOCP tras muchas pruebas de estabilidad y rendimiento. Por eso a veces, cuando intentas “mejorarlos” manualmente (bajando valores a lo loco), el resultado es una mezcla rara de inestabilidad, errores en MemTest o incluso pérdidas de rendimiento en pruebas sintéticas como AIDA64 o membench.

Hay que tener claro que, mientras los tiempos principales sean correctos, estos subtimings afinan detalles de cómo se reparte el trabajo entre bancos y filas de memoria. Ajustarlos puede marcar milésimas o pequeños porcentajes en benchmarks, pero la prioridad absoluta es que el sistema sea estable en todas las cargas: juegos, edición, tests prolongados, etc.

El papel de tRFC: refresco de filas de memoria

El timing tRFC (Row Refresh Cycle Time) es uno de los más importantes entre los secundarios. Controla el tiempo mínimo que debe esperar la RAM para completar una operación de refresco de fila. Como los chips DRAM pierden carga con el tiempo, necesitan refrescar su contenido periódicamente para no perder datos; tRFC determina cuánto se “bloquea” una fila mientras se hace ese refresco.

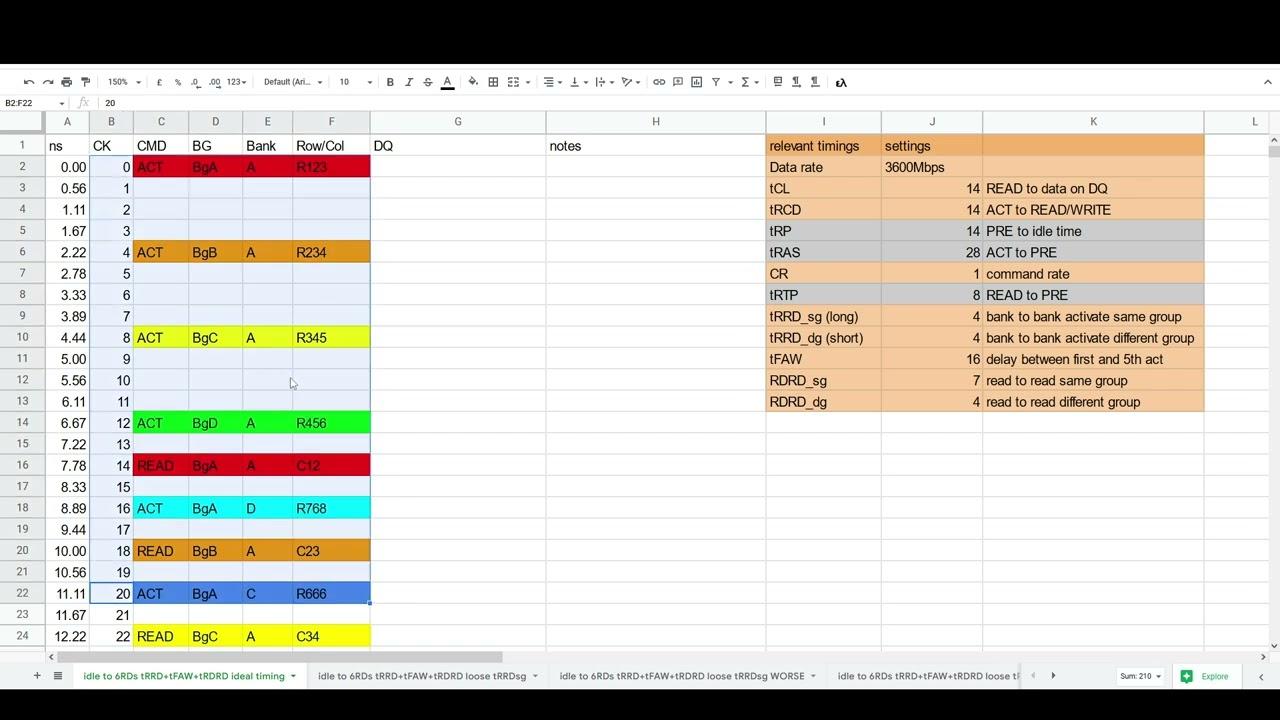

En algunas BIOS verás varios campos relacionados: tRFC (en ciclos), tRFC (ns), tRFC2 y tRFC4. El valor en nanosegundos es el tiempo real, y los otros se expresan en ciclos de reloj internos. En un caso práctico de una ASUS ROG Strix G15 Advantage Edition, la RAM de serie y una RAM Crucial DDR4 3200 MHz CL22 tenían exactamente los mismos valores de refresco:

- tRFC (ns) – 350

- tRFC – 560

- tRFC2 – 416

- tRFC4 – 256

Aunque la RAM nueva era de doble cara y con mejores subtimings en otros campos, el refresco estaba fijado en los mismos valores seguros. Esto es bastante habitual: el fabricante prioriza estabilidad a largo plazo, especialmente en portátiles o equipos que van a estar muchas horas encendidos.

Existe incluso una regla muy usada en la comunidad de overclocking para relacionar estos tiempos: tRFC2 ≈ tRFC × 0,768 y tRFC4 ≈ tRFC × 0,46. Son proporciones orientativas que ayudan a mantener coherencia entre los distintos parámetros de refresco cuando se ajusta manualmente el valor base.

Para calcular un tRFC aproximado en ciclos a partir de un valor estimado en nanosegundos, muchos entusiastas siguen una fórmula sencilla: tRFC (ciclos) ≈ (tRFC_ns × frecuencia de la memoria) / número de canales. Por ejemplo, para 180 ns a 3600 MHz en doble canal: 0,18 × 3600 / 2 = 324 ciclos. Este tipo de cálculos sirve para orientarse, pero luego hay que validar con tests de estabilidad.

tFAW: limitador de activaciones en ventana de tiempo

El parámetro tFAW (Four Activate Window) es de los que más confunden. Define una ventana de tiempo en la que solo se puede realizar un número máximo de activaciones de fila dentro de un mismo rank, normalmente cuatro. Es una especie de “semáforo” que evita que el chip se sobrecargue abriendo demasiadas filas de golpe.

Una regla bastante conocida en comunidades de overclock (y que varios usuarios atribuyen a guías coreanas de foros como OCN) indica que tFAW debería ser, como norma general, cuatro veces tRRDS. Es decir, si tRRDS está en 4, un tFAW alrededor de 16 sería un valor muy ajustado. En la práctica, las memorias comerciales suelen llevar tFAW bastante más alto (40, 44, 48…) para garantizar margen de seguridad.

Se ha observado en varias pruebas que, al bajar tFAW por debajo de cierto punto, el rendimiento empieza a empeorar en lugar de mejorar. Un usuario que estaba afinando su kit con XMP II comprobó que:

- Al llevar tFAW de 44 a 40, la escritura mejoró ligeramente (dentro del margen de error).

- Al seguir reduciendo tFAW por debajo de 40, las velocidades de lectura/escritura y la latencia se degradaban.

Otro caso, con un kit Patriot Viper Steel a alta frecuencia, mostró un efecto aún más claro: pasar tFAW y tWR de 12 a 24 “por seguridad” desplomó el rendimiento en membench, pese a que pruebas de memoria no marcaban errores. Cuando el usuario volvió a valores más agresivos y ajustó bien otros subtimings como tRFC, obtuvo benchmarks mucho mejores sin perder estabilidad.

Conclusión práctica: tFAW no es un simple “cuanto más bajo mejor”. Tiene que guardar relación con tRRDS y el diseño interno del kit. Valores demasiado altos o demasiado bajos acaban limitando el rendimiento, aunque la memoria pase pruebas básicas de error.

tRRD y tRRDL: tiempo mínimo entre activaciones de fila

Los timings tRRD (Row to Row Delay) y tRRDL (Row to Row Delay Long) marcan el intervalo mínimo entre activaciones de filas en distintos bancos. tRRDS suele referirse a la distancia corta (Short) y tRRDL a la larga (Long), que entra en juego cuando la activación afecta a bancos más alejados dentro del chip.

En la práctica, estos parámetros limitan cuán rápido la controladora de memoria puede ir saltando entre distintas filas para atender solicitudes. Si los pones demasiado bajos, te puedes encontrar con inestabilidad o con que otros mecanismos de seguridad (como tFAW) entren a frenar el ritmo.

En el ejemplo de la ASUS ROG Strix G15, al cambiar de la RAM de serie a un kit Crucial DDR4 3200 MHz CL22 de doble rango se produjo esta diferencia:

- De serie: tRRDS 9, tRRDL 11, tFAW 48, tSTAG 12.

- RAM nueva: tRRDS 4, tRRDL 8, tFAW 34, tSTAG 9.

Aunque los tiempos principales no cambiaban, los subtimings eran claramente más agresivos en la RAM Crucial. Aun así, en uso real (juegos y productividad) las diferencias de rendimiento eran mínimas. El cambio se notaba más en benchmarks sintéticos que en el día a día.

Otro usuario que estaba ajustando su perfil XMP II se encontró con una situación curiosa con tRRDL: al bajar tRRDL de su valor inicial, los resultados de lectura, escritura y latencia se movían arriba y abajo dentro del margen de error. Con tRRDL ajustado a 8 o 9, los resultados eran prácticamente equivalentes a la configuración base; al reducirlo aún más, el rendimiento empezaba a empeorar. Es decir, hay un punto óptimo a partir del cual seguir apretando ya no ayuda.

En muchas guías avanzadas se recomienda que tRRDL no se fuerce demasiado por debajo de los valores propuestos por el perfil XMP, especialmente con módulos de doble rango (DR), donde los requisitos eléctricos son mayores. El propio comportamiento del sistema acaba “pagando” los excesos, a veces con una disminución del rendimiento que parece ilógica sobre el papel.

Qué es tSTAG y por qué apenas se habla de él

tSTAG es uno de esos subtimings que suelen aparecer en BIOS avanzadas y que casi nadie toca. Suele referirse a una especie de retardo de “staggering” o escalonado entre ciertos comandos internos, pensado para evitar conflictos de señales cuando se encadenan determinadas operaciones.

En el ejemplo práctico de la RAM del portátil ASUS, el paso de la memoria de serie a la Crucial cambió tSTAG de 12 a 9. Es un ajuste algo más agresivo, pero que en la práctica no produjo un salto medible en benchmarks cotidianos. Este tipo de subtiming se ajusta más por requisitos internos del chip y de la controladora que por impacto directo en el rendimiento.

Por eso muchos expertos en foros coinciden en que la prioridad a la hora de hacer overclock es centrarse en los tiempos principales y en los subtimings clave como tRFC, tFAW, tRRD, tWTR o tWR. Parámetros como tSTAG suelen dejarse a merced del auto de la BIOS o de los valores definidos por el fabricante.

Aunque se puede experimentar con ellos si se busca exprimir el último 1 % de rendimiento, no son el primer sitio donde mirar si lo que quieres es una mejora clara para jugar o para acelerar tareas de productividad. El riesgo de provocar inestabilidades raras sin ganar nada apreciable suele superar el beneficio potencial.

Relaciones y reglas básicas entre temporizaciones

Quien haya buceado en foros de overclock habrá visto montones de reglas y fórmulas para relacionar timings. Algunas de las más repetidas se basan en experiencias acumuladas de la comunidad, como las que un usuario recogió de un conocido “ingeniero” coreano en OCN. Estas reglas no son leyes grabadas en piedra, pero sirven como punto de partida.

También hay varias formas habituales de calcular tRAS:

- tRP + tRAS ≈ tRC

También hay varias formas habituales de calcular tRAS:

- tRAS ≈ tRCD + tCL (la más usada).

- tRAS ≈ tCL + tRP.

- tRAS ≈ tRCD + tWR + tBL (tBL es el Burst Length).

Sobre tWR (Write Recovery Time), hay una serie de “reglas” para que no quede excesivamente bajo:

- tWR ≥ tRRDS + tWTRS

- tWR ≥ tCL + tRTP

- tWR ≥ tRAS − tRCD

Si no se respetan estas relaciones mínimas, el sistema puede pasar algunos tests ligeros pero fallar bajo cargas más pesadas o tras varias horas de uso. Es lo típico de “parece estable, pero el juego se cuelga al cabo de un rato”.

Otro grupo interesante de relaciones afecta a tRDWR (Read to Write Delay). En algunas configuraciones se usa la referencia:

- tRDWR ≈ tRCD_RD / 2 como valor base.

A partir de ahí se consideran ciertos valores “seguros” según si la RAM es de un solo rango (SR) o doble rango (DR):

- 2× SR: tRDWR = tRCD_RD / 2

- 4× SR: tRDWR = tRCD_RD / 2 + 1

- 2× DR: tRDWR = tRCD_RD + 2

- 4× DR: tRDWR = tRCD_RD + 4 (hay quien comenta que el valor +3 puede permitir usar un tWRRD más bajo).

Todo esto son guías para no entrar en combinaciones absurdas. Se puede salir un poco de estas reglas para afinar, pero cuanto más te alejas, más probables son los errores sutiles que solo aparecen después de muchas horas de estrés o en ciertas aplicaciones.

tWR, tWTR, tRTP y tCWL: subtimings que sí pueden notarse

Además de tRFC, tFAW y tRRD, hay otros subtimings muy relevantes en el comportamiento de la RAM: tWR, tWTRS, tWTRL, tRTP y tCWL. Varios usuarios han compartido experiencias concretas donde tocar estos valores ha cambiado de forma clara tanto estabilidad como rendimiento.

tWR (Write Recovery Time) marca el tiempo que debe esperar la memoria después de una escritura antes de poder ejecutar ciertas operaciones posteriores. En el caso de un usuario que siguió la DRAM Calculator para relajar tFAW y tWR de 12 a 24, el efecto fue llamativo: la memoria se volvió estable en pruebas como MemTest86, pero los tiempos en membench se dispararon a peor de forma brutal. Es decir, había ganado estabilidad, pero a costa de matar el rendimiento.

Cuando ese mismo usuario volvió a tiempos más agresivos y afinó en paralelo otros parámetros como tRFC, tRFC2 y tRFC4, consiguió una configuración con CL15, tRCDRD 16 y subtimings muy apretados, estable en múltiples pasadas de memtest y Karhu. Incluso subió ligeramente VDDP y VDDG hasta 0,9 V y 0,95 V para ajustarse a los mínimos recomendados, manteniendo el voltaje de la RAM en torno a 1,38 V y el SoC en 1,1 V.

En cuanto a tWTR (Write to Read), se suele dividir en tWTRS (Short) y tWTRL (Long). Una recomendación extendida es que tWTRL sea el doble o el triple de tRRDS, de forma que haya suficiente margen entre escrituras y lecturas para no forzar demasiado los bancos. De nuevo, es más una guía práctica que una norma rígida, pero ayuda a evitar combinaciones problemáticas.

tRTP (Read to Precharge) y tCWL (CAS Write Latency) también juegan su papel. Hay una pauta bastante común: tCWL suele igualarse a tCL. Si no coinciden, a menudo se busca que la diferencia sea de un paso lógico, subiendo o bajando un valor para mantener la coherencia. Bajar tCWL demasiado puede causar inestabilidad sin una mejora real medible fuera de benchmarks muy específicos.

Redactor apasionado del mundo de los bytes y la tecnología en general. Me encanta compartir mis conocimientos a través de la escritura, y eso es lo que haré en este blog, mostrarte todo lo más interesante sobre gadgets, software, hardware, tendencias tecnológicas, y más. Mi objetivo es ayudarte a navegar por el mundo digital de forma sencilla y entretenida.