- Clockless security se relaciona con diseños de CPU asíncronos, donde se reduce o elimina la dependencia de un reloj global.

- Los procesadores modernos combinan cachés, MMU, paralelismo e hilos múltiples, lo que complica a la vez el rendimiento y la protección.

- Los diseños sin reloj pueden mitigar ataques por temporización, pero exigen nuevas formas de monitorización y auditoría hardware.

- Virtualización, vCPU y aceleradores especializados amplían la superficie de ataque, haciendo esencial integrar seguridad desde el silicio.

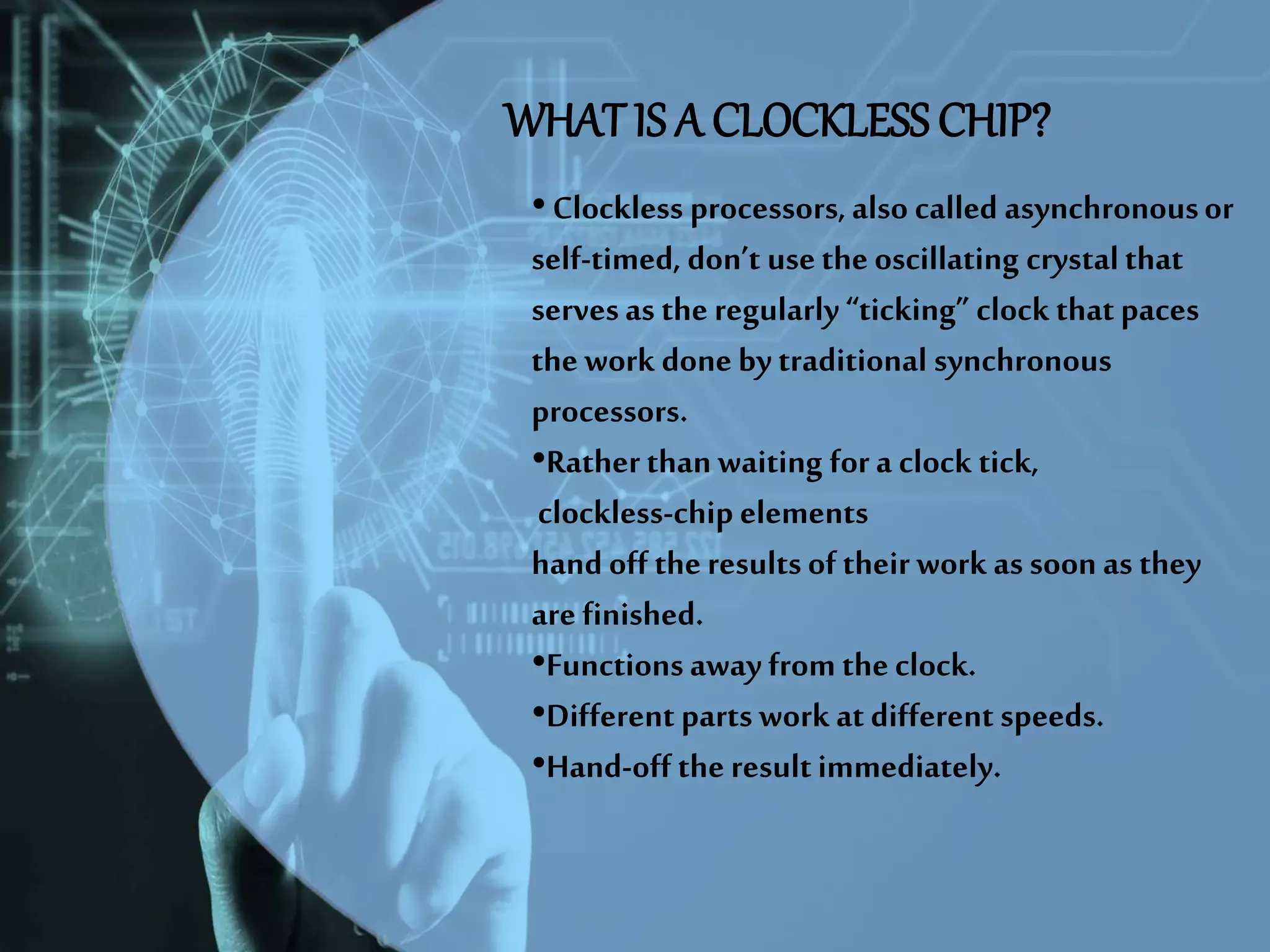

La expresión clockless security suena a concepto futurista, pero en realidad está muy ligada a cómo se diseñan y protegen los procesadores y sistemas actuales. Para entenderla bien hay que bajar al nivel de cómo funciona una CPU por dentro, cómo se organiza la ejecución de instrucciones y qué papel juega la famosa señal de reloj que marca el ritmo de todo el sistema.

En las últimas décadas los procesadores han vivido una carrera por subir la frecuencia de reloj, integrar más transistores y multiplicar su paralelismo. A la vez, han ido apareciendo diseños que intentan liberarse de la dependencia del reloj global, bien sea en todo el chip o en partes concretas. Ese terreno, el de los diseños asíncronos o sin reloj global, abre oportunidades muy interesantes en consumo y disipación térmica… y también retos específicos de seguridad que se engloban a menudo bajo la idea de clockless security.

La CPU como centro del sistema y su relación con el reloj

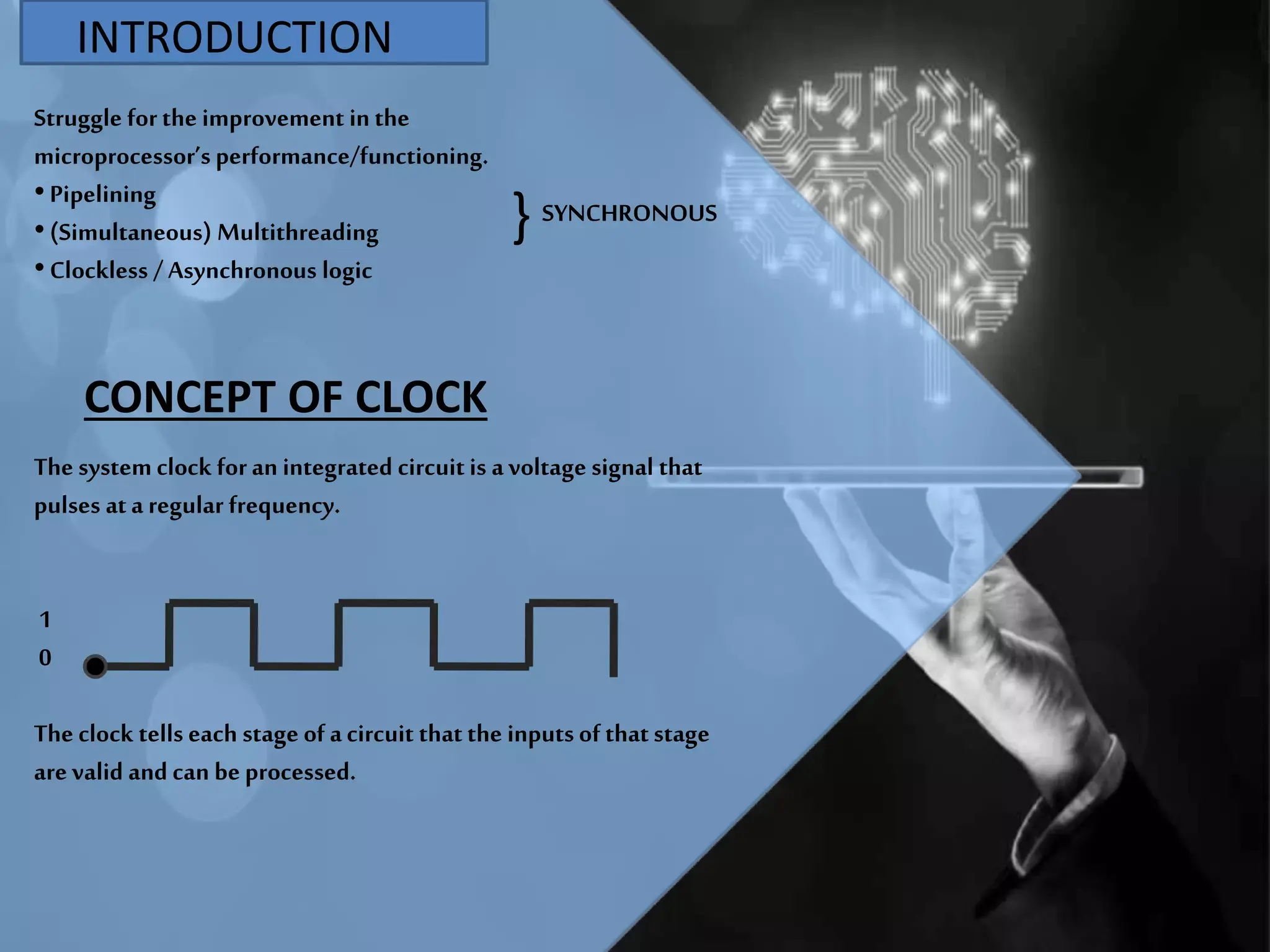

Cuando hablamos de seguridad ligada al reloj, lo primero es recordar qué es exactamente una CPU. En esencia, la unidad central de proceso es el cerebro del ordenador: el componente que interpreta y ejecuta las instrucciones de los programas, coordina memoria, entrada/salida y coprocesadores especializados como las GPU.

Dentro de una CPU moderna encontramos varios bloques bien diferenciados. Por un lado está la unidad aritmético-lógica (ALU), encargada de las operaciones matemáticas y lógicas con números enteros. Por otro, los registros, que son pequeñas memorias ultrarrápidas donde se almacenan los datos con los que está trabajando en ese momento el procesador. Y encima de todo, una unidad de control que decide, ciclo a ciclo, qué se hace, qué se lee de memoria y qué se escribe.

La mayoría de procesadores actuales son diseños síncronos. Eso significa que todos esos bloques internos se coordinan usando una señal de reloj periódica, una especie de metrónomo electrónico que marca el ritmo de ejecución. Cada flanco de ese reloj avanza un paso del llamado ciclo de instrucción: se captura la instrucción, se descodifica, se ejecuta, se guardan los resultados, y vuelta a empezar.

En un procesador clásico, el reloj se genera mediante un oscilador externo que envía millones o miles de millones de pulsos por segundo. La frecuencia de esos pulsos en hertzios, megahercios o gigahercios nos indica cuántos “tics” tiene disponibles la CPU cada segundo para mover datos y realizar operaciones. A mayor frecuencia de reloj, más trabajo potencial por segundo, siempre que el resto de la arquitectura acompañe.

Así, el rendimiento no depende solo del reloj, sino también de cuántas instrucciones por ciclo (IPC) es capaz de completar el procesador. El producto de frecuencia por IPC nos da una idea de los millones de instrucciones por segundo que puede ejecutar, aunque las cifras teóricas suelen ser mucho más optimistas que lo que luego se ve con programas reales.

Del cableado fijo a los microprocesadores integrados

Para poner en contexto los diseños sin reloj es útil repasar cómo ha evolucionado la CPU. Los primeros ordenadores electrónicos, como el ENIAC, eran máquinas de programa fijo cableado: para cambiar de tarea había que recablear físicamente el sistema. La idea revolucionaria fue el ordenador de programa almacenado, en el que las instrucciones residen en memoria; el procesador simplemente las va leyendo y ejecutando.

Esa arquitectura de programa almacenado asociada a John von Neumann se acabó imponiendo. En ella, instrucciones y datos comparten el mismo espacio de memoria, a diferencia de la arquitectura Harvard, que separa físicamente ambos tipos de información. Hoy casi todas las CPU de propósito general siguen una arquitectura tipo von Neumann, aunque en el mundo embebido sigue habiendo muchos procesadores Harvard puros o híbridos.

Los primeros procesadores se construían con relés o tubos de vacío. Eran voluminosos, lentos y con una fiabilidad muy limitada. El salto al transistor de estado sólido en los años 50 y 60 permitió incrementar radicalmente la velocidad y reducir el consumo y el tamaño. A partir de ahí se pasó de circuitos discretos a circuitos integrados (IC), metiendo cada vez más transistores en una única pastilla.

Con la aparición del circuito integrado, primero de pequeña escala (SSI), luego media escala (MSI), gran escala (LSI) y finalmente muy gran escala (VLSI), la CPU se fue comprimiendo hasta caber entera en uno o unos pocos chips. Esa integración culminó con el microprocesador, en el que la unidad de proceso completa se fabrica en una sola pastilla de silicio.

El Intel 4004, lanzado en 1971, fue uno de los primeros microprocesadores comerciales. Muy pronto llegaron diseños más potentes como el Intel 8080, que se convirtieron en la base de los ordenadores personales. A partir de ese momento, el término CPU empezó a usarse casi siempre para referirse a estos microprocesadores.

Componentes internos clave de una CPU moderna

Las CPU actuales dedican una parte enorme de su superficie de silicio a elementos auxiliares pensados para sacar el máximo partido a cada ciclo de reloj. Por ejemplo, casi todo procesador incorpora varios niveles de caché: memorias pequeñas pero muy rápidas situadas cerca de los núcleos que guardan copias de los datos más usados para no tener que ir constantemente a la RAM.

Además de las cachés L1, L2 y a menudo L3, una CPU compleja incluye una unidad de gestión de memoria (MMU) que traduce direcciones virtuales (las que maneja el sistema operativo) en direcciones físicas de la RAM, gestiona la memoria virtual y proporciona aislamiento entre procesos.

En el plano de cálculo tenemos varias unidades de ejecución especializadas: la ALU para enteros, la unidad de coma flotante (FPU) para operaciones con decimales, unidades de generación de direcciones (AGU) para calcular posiciones de memoria de forma rápida y, en muchas arquitecturas, unidades vectoriales o SIMD para operar de golpe sobre varios datos en paralelo.

También hay una unidad de control, que puede ser de lógica cableada o estar basada en microcódigo, es decir, un programa interno que traduce cada instrucción de alto nivel en una secuencia de señales de control internas. En muchos procesadores ese microcódigo se puede actualizar, lo que permite corregir errores de diseño o ajustar el comportamiento a posteriori.

Por último, hay una batería de registros internos: de propósito general, acumuladores, contadores de programa, registros de estado con banderas (flags) que indican cosas como si el resultado de una operación es cero, negativo o ha producido un desbordamiento, etc. Todo esto se coordina siguiendo el clásico ciclo de captura, decodificación y ejecución de instrucciones.

Cómo se ejecuta un programa paso a paso

El funcionamiento básico de cualquier CPU se reduce a ir tomando instrucciones de memoria y procesarlas una detrás de otra. Esto sucede siguiendo tres grandes fases. Primero, la etapa de captura (fetch), en la que se lee de memoria la instrucción cuyo direccionamiento viene dado por el contador de programa.

Después llega la fase de decodificación. La instrucción recién capturada pasa a través de un decodificador binario que examina su código de operación (opcode) y traduce ese patrón de bits en señales concretas que habilitan o deshabilitan partes del procesador. Ahí se decide si es una suma, un salto, una carga desde memoria, etc., y qué registros o direcciones intervienen.

Por último, se ejecuta la operación. La ALU o la unidad correspondiente realiza el cálculo o movimiento de datos, y el resultado se guarda normalmente en un registro o en memoria. Si hay que alterar el flujo del programa, por ejemplo con un salto condicional, el contador de programa se actualiza con una nueva dirección. Ese juego de instrucciones, datos y saltos es el que termina formando bucles, funciones, condicionales y toda la lógica de nuestros programas.

En los procesadores sencillos todo sucede de forma lineal y secuencial. Pero en las CPU modernas se intentan solapar muchas de estas etapas usando técnicas de paralelismo. El objetivo es que cada ciclo de reloj se esté haciendo el máximo trabajo posible y el hardware no se quede de brazos cruzados.

Paralelismo, canalización y ejecución fuera de orden

Para no desaprovechar el reloj, los diseñadores introdujeron la canalización de instrucciones (pipelining). Se divide el camino de datos en varias etapas, de manera similar a una cadena de montaje. Mientras una instrucción está siendo decodificada, la siguiente ya se está capturando de memoria y otra distinta puede estar ejecutándose en la ALU.

El problema es que a veces una instrucción necesita el resultado de otra que todavía no ha terminado. Eso genera dependencias de datos y obliga a introducir burbujas o esperas en la canalización. Para minimizar estos parones se inventaron técnicas como el reenvío de operandos, la predicción de saltos y, más tarde, la ejecución fuera de orden, en la que el procesador reordena internamente las instrucciones siempre que se respete el resultado final del programa.

El siguiente paso fue el diseño superscalar: dotar al procesador de varias unidades de ejecución del mismo tipo para poder lanzar varias instrucciones por ciclo de reloj, siempre que no haya conflictos entre ellas. Un despachador interno analiza el flujo de instrucciones, detecta qué puede ejecutarse en paralelo y las distribuye entre las distintas unidades.

Todos estos trucos se engloban dentro del llamado paralelismo a nivel de instrucción (ILP). El límite práctico de estas técnicas y la creciente dificultad para seguir subiendo la frecuencia de reloj sin disparar consumo y calor hicieron que, a partir de cierto punto, los fabricantes empezaran a apostar también por el paralelismo a nivel de tareas: varios hilos y varios núcleos por chip (y mecanismos como el parking de núcleos).

Así nacen los procesadores multinúcleo y las arquitecturas con multithreading por hardware, donde cada núcleo puede mantener el estado de varios hilos de ejecución y cambiar de uno a otro con rapidez para aprovechar mejor los recursos internos mientras unos hilos esperan datos de memoria.

El papel de la frecuencia de reloj y sus límites físicos

Volviendo al reloj, hay que tener en cuenta que la señal que sincroniza el procesador es, al final, una señal eléctrica que se propaga por el chip. A medida que las frecuencias suben y el número de transistores aumenta, mantener esa señal perfectamente alineada en todas partes se vuelve muy difícil. Aparecen problemas de distribución de reloj, de desfases y de integridad de señal.

Por otro lado, cada transición del reloj hace que multitud de transistores cambien de estado, incluso si cierta zona del procesador no está haciendo nada útil en ese instante. Eso se traduce en consumo de energía y calor disipado simplemente por mantener el metrónomo en marcha. Para aliviarlo se introdujeron técnicas como el clock gating, que apaga selectivamente la señal de reloj en bloques que no se usan, reduciendo el gasto energético.

Sin embargo, a partir de cierto umbral subir la frecuencia deja de ser razonable: los problemas de consumo, temperatura y distribución de reloj se disparan. Ese cuello de botella es una de las razones por las que se ha explorado la idea de prescindir, total o parcialmente, de un reloj global: es aquí donde entran en juego los diseños asíncronos o “clockless”.

En un diseño asíncrono, en vez de tener un único reloj que marca el tiempo para todo el chip, son los propios datos y señales de control los que sincronizan las operaciones. Los bloques se comunican mediante protocolos de petición y reconocimiento (handshaking): cuando un dato está listo, el productor avisa al consumidor, y este reacciona sin esperar a un flanco de reloj fijo.

Se han construido procesadores completamente asíncronos compatibles con conjuntos de instrucciones conocidos, como la familia AMULET basada en ARM o proyectos derivados de MIPS. También hay diseños híbridos, donde solo ciertas unidades (por ejemplo, una ALU concreta) funcionan sin reloj global, mientras el resto del procesador sigue siendo síncrono.

Qué entendemos por clockless security

Cuando se habla de clockless security se mezclan dos ideas: por un lado, el diseño asíncrono como técnica para reducir consumo y calor; por otro, la implicación de prescindir del reloj a la hora de analizar, monitorizar y proteger el comportamiento del sistema frente a ataques o fallos.

En los sistemas síncronos, muchas herramientas de seguridad y monitorización se apoyan en la existencia de un ritmo temporal estable y predecible. Resulta relativamente sencillo contar ciclos, medir cuánto tarda cierta operación o intentar detectar comportamientos anómalos midiendo variaciones en tiempos que deberían ser constantes.

En un sistema asíncrono o parcialmente sin reloj, esas referencias temporales rígidas se diluyen. El tiempo de ejecución de una operación puede depender de la disponibilidad real de datos, de la congestión en determinadas rutas internas o de pequeñas variaciones físicas. Desde el punto de vista del atacante, esto puede hacer más difícil montar ataques de canal lateral basados en temporización, porque desaparece el reloj global que sirve como referencia común.

Sin embargo, ese mismo carácter dinámico también complica la vida a quien quiere observar y auditar el sistema por dentro. Muchas sondas y contadores de hardware están pensados para trabajar a partir de ciclos de reloj; si no hay un reloj global claro, medir rendimiento y detectar actividades sospechosas pasa a requerir otras métricas y mecanismos.

Además, el diseño asíncrono, al liberarse del reloj, hace que los caminos de datos puedan activarse en momentos ligeramente distintos en cada ejecución, lo que potencialmente aleatoriza las fugas temporales pero también podría abrir otras puertas, por ejemplo en forma de patrones de consumo de energía distintos y más complejos que podrían ser explotados por ataques de análisis de potencia.

Representación de datos, tamaño de palabra y seguridad

Otro factor importante relacionado con la arquitectura de la CPU es cómo representa y maneja los datos. Casi todos los procesadores modernos usan representación binaria, con valores de tensión que corresponden a 0 y 1. El tamaño de palabra (8, 16, 32, 64 bits…) determina el rango de enteros que se pueden manejar directamente y la cantidad de memoria direccionable.

Desde el punto de vista de la seguridad, el tamaño de palabra afecta al espacio de direcciones y a la probabilidad de colisiones, desbordamientos y errores de puntero. Un sistema de 32 bits con 2^32 direcciones posibles tiene limitaciones muy claras frente a uno de 64 bits. Además, muchos mecanismos de protección modernos, como ciertas extensiones de memoria protegida, se apoyan en disponer de espacio de direcciones amplio.

El uso de MMU y traducción de direcciones introduce también una capa extra entre el programa y la memoria física, algo crucial para aislar procesos, implementar memoria virtual y proteger el kernel. En contextos asíncronos, la coordinación entre estas traducciones y las señales de mano entre bloques sin reloj debe estar muy bien diseñada para no crear agujeros de seguridad o condiciones de carrera.

A su vez, las extensiones vectoriales (SIMD) y las unidades de coma flotante permiten trabajar con grandes volúmenes de datos en paralelo. Esto es un arma de doble filo: por un lado, acelera algoritmos criptográficos y tareas de análisis; por otro, si se explota de forma maliciosa, proporciona una gran capacidad de cálculo para romper cifrados débiles o lanzar ataques de fuerza bruta.

En un escenario clockless o parcialmente asíncrono, la forma en que se programan y protegen esas unidades de cálculo paralelo debe tener en cuenta que los patrones de ejecución y consumo ya no siguen un ritmo fijo marcado por el reloj, sino que responderán a la dinámica real de los datos, lo que también influye en el diseño de contramedidas frente a canales laterales.

Paralelismo masivo, multihilo y vectores: impacto en clockless security

Los procesadores modernos persiguen aumentar el rendimiento no solo subiendo la frecuencia, sino ejecutando más trabajo en paralelo. Eso implica varios núcleos, multihilo por hardware y unidades vectoriales capaces de procesar múltiples datos por instrucción. A todo esto se suma el auge de los aceleradores específicos como GPU, DSP o TPU.

Desde la perspectiva de la seguridad, cada nuevo bloque de ejecución y cada nuevo nivel de paralelismo es una superficie adicional que proteger. Hay que coordinar la coherencia de cachés, la gestión de memoria compartida, los mecanismos de exclusión mutua y evitar condiciones de carrera y fugas de información entre hilos o procesos concurrentes.

En entornos clockless o híbridos, esa coordinación se basa más en protocolos de comunicación entre bloques que en ciclos de reloj globales. Por ejemplo, un núcleo puede usar señales de petición y reconocimiento para acceder a memoria o a un recurso compartido, y el retardo efectivo dependerá del tráfico real en ese momento, no de un número fijo de ciclos.

Ese comportamiento, visto desde el exterior, dificulta ciertos ataques que se apoyan en mediciones de tiempo muy precisas en función del número de ciclos de reloj gastados. Pero a la vez, los diseñadores de seguridad tienen que ir más allá del conteo de ciclos y apoyarse en contadores de eventos, medición de tráfico, consumo de energía y otras señales para detectar comportamientos sospechosos.

Por eso muchos fabricantes integran contadores de rendimiento hardware, que permiten monitorizar en tiempo real cosas como fallos de caché, predicciones de salto fallidas, accesos a memoria concretos, etc. Estos contadores, bien utilizados, son una herramienta potente tanto para optimizar rendimiento como para encontrar patrones anómalos propios de malware o de exploits avanzados, incluso en arquitecturas parcialmente asíncronas.

Virtualización, vCPU y aislamiento en entornos modernos

Otro ingrediente clave del panorama actual es la virtualización. En la nube trabajamos constantemente con CPU virtuales (vCPU), que son fragmentos lógicos de capacidad de proceso asignados a máquinas virtuales o contenedores encima de un hardware físico compartido.

Cada vCPU es, en esencia, un conjunto de hilos o tiempos de ejecución que el hipervisor agenda sobre los núcleos reales. Para que esto funcione bien, la CPU física ofrece modos privilegiados especiales que permiten a los hipervisores crear y aislar máquinas virtuales, interceptar ciertas instrucciones sensibles y gestionar la memoria de cada huésped sin que puedan estorbarse o espiarse entre sí.

En este contexto, clockless security implica que el propio reparto del tiempo de CPU entre máquinas virtuales no depende solo de un reloj uniforme, sino de mecanismos de planificación más dinámicos respaldados por el hardware. El hipervisor sigue viendo ciclos de reloj, pero la forma en que esos ciclos se convierten en trabajo efectivo en cada núcleo puede verse alterada por bloques asíncronos internos.

Desde el punto de vista de la protección, esto obliga a diseñar herramientas de monitorización que no se limiten a contar ticks, sino que sepan leer los contadores de rendimiento, las estadísticas de uso y los eventos de bajo nivel para detectar abuso de recursos, escapes de máquina virtual o patrones irregulares que apunten a una intrusión.

Además, en entornos de cómputo intensivo, donde se explotan al máximo las unidades vectoriales, las GPU y otros aceleradores, los responsables de seguridad deben contemplar que esos bloques, sean síncronos o asíncronos, pueden convertirse en instrumentos para acelerar ataques criptográficos, minar criptomonedas a espaldas del usuario o realizar análisis de grandes volúmenes de datos robados.

Rendimiento, consumo y overclocking frente a diseño sin reloj

Por último, hay que poner sobre la mesa la relación entre rendimiento y consumo. Subir la frecuencia de reloj mediante overclocking (por ejemplo, realizando un test de estabilidad con OCCT) permite que una CPU realice más operaciones por segundo, pero a cambio aumenta mucho su consumo y temperatura. De hecho, muchos procesadores actuales ya ajustan dinámicamente su frecuencia y voltaje según la carga de trabajo y la temperatura interna.

Los diseños asíncronos ofrecen una alternativa: en lugar de usar un reloj muy rápido e intentar mantener todo en fase, dejan que cada bloque funcione al ritmo que marcan los datos. En momentos de poca carga, las partes inactivas apenas cambian de estado, lo que reduce el consumo sin necesidad de complejos mecanismos de gestión de energía basados en el reloj.

Desde el prisma de la seguridad, menos consumo y menos calor no es solo una cuestión ecológica o de factura eléctrica. También significa menor estrés para los componentes, menos probabilidad de fallos inducidos por electromigración o fugas de corriente, y potencialmente menor exposición a ataques que intenten explotar el comportamiento del sistema bajo condiciones extremas de temperatura o voltaje.

Sin embargo, diseñar un sistema totalmente asíncrono y seguro no es trivial. Se necesita una verificación muy rigurosa de los protocolos de comunicación entre bloques, de las condiciones de carrera y de los estados intermedios para que no se produzcan comportamientos no deterministas aprovechables por un atacante. La complejidad del diseño, la escasez de herramientas maduras y la necesidad de compatibilidad hacia atrás con software existente han hecho que, de momento, la mayoría de procesadores comerciales sigan siendo mayoritariamente síncronos con pequeñas islas asíncronas.

La combinación de todos estos factores -arquitectura interna, gestión del reloj, paralelismo, virtualización y energía- hace que la seguridad en entornos sin reloj global sea un equilibrio delicado. Los diseños asíncronos permiten mitigar ciertos tipos de ataque basados en temporización y facilitar estrategias de ahorro energético muy finas, pero también plantean desafíos nuevos a la hora de monitorizar, auditar y verificar el comportamiento del hardware, de modo que la clave está en integrar mecánicas de observabilidad y aislamiento robustas desde el propio silicio hasta el software de más alto nivel.

Redactor apasionado del mundo de los bytes y la tecnología en general. Me encanta compartir mis conocimientos a través de la escritura, y eso es lo que haré en este blog, mostrarte todo lo más interesante sobre gadgets, software, hardware, tendencias tecnológicas, y más. Mi objetivo es ayudarte a navegar por el mundo digital de forma sencilla y entretenida.