- Un Makefile bien diseñado permite automatizar la compilación, gestionar dependencias y facilitar tareas como limpieza y empaquetado, optimizando el flujo de trabajo en proyectos de software.

- El uso de variables, reglas implícitas, objetivos especiales y la correcta declaración de dependencias incrementa la eficiencia y la mantenibilidad, permitiendo ampliar el proyecto sin complicaciones.

- Alternativas como CMake ofrecen gestión multiplataforma y automatización avanzada, pero dominar Makefile sigue siendo esencial para programadores en entornos Unix y para comprender a fondo los procesos de construcción.

En el mundo de la programación y el desarrollo de software, optimizar el proceso de compilación y gestión de proyectos es esencial, sobre todo cuando el número de archivos crece y empiezan a aparecer dependencias complejas. Aquí es donde el uso de herramientas como make y la elaboración de archivos Makefile adquieren un papel protagonista. Si alguna vez te has preguntado cómo automatizar la generación de binarios en tus proyectos de C o C++, o simplemente quieres facilitar la vida a quien trabaje con tu código, dominar los secretos de los Makefile se convierte en una necesidad casi obligatoria.

En este extenso artículo verás, paso a paso y de manera exhaustiva, cómo crear y personalizar tus propios Makefile independientemente del tamaño de tu proyecto, desde los ejemplos más básicos hasta configuraciones mucho más avanzadas, abarcando tanto la teoría esencial como consejos prácticos, trucos para evitar errores comunes y alternativas modernas como CMake. El objetivo es que, cuando termines de leer, tengas una visión clara y completa de cómo funciona make, por qué es tan útil y cómo puedes sacarle el máximo partido ajustándolo a tus necesidades reales de desarrollo.

¿Qué es make y para qué sirve un Makefile?

make es una de las utilidades más veteranas y versátiles del universo Unix/Linux, aunque también existen implementaciones para otros sistemas operativos como Windows (NMAKE, entre otros). Su propósito principal es gestionar la automatización de la compilación y construcción de proyectos, especialmente cuando están compuestos por múltiples archivos fuente, librerías y cabeceras. El fichero Makefile es el guion donde queda plasmada la lógica de construcción del proyecto: define qué debe hacerse, en qué orden y con qué dependencias, permitiendo que el propio make sólo ejecute las tareas necesarias cuando haya cambios.

Imagina el problema típico: tienes un proyecto con decenas de ficheros .c y .h. Si lo compilas «a mano», el proceso es lento, tedioso y es fácil cometer errores olvidando algún parámetro, dependencia o re-compilando todo de nuevo cada vez. Con make y un Makefile bien diseñado, la compilación se vuelve casi un paseo, ya que sólo se regeneran los componentes que realmente lo necesitan, ahorrando tiempo y quebraderos de cabeza. Además, el Makefile no sólo sirve para compilar: se puede usar para limpiar archivos temporales, empaquetar el código, instalar binarios, ejecutar tests y mucho más.

Ventajas de usar un Makefile en tus proyectos

- Automatización de la compilación: Olvida las largas líneas manuales de comandos para compilar. Con un simple «make», el sistema sabe qué tiene que hacer.

- Gestión de dependencias: Solo compila lo que ha cambiado o depende de los archivos modificados, ahorrando tiempo.

- Mayor portabilidad y facilidad para otros desarrolladores: Cualquiera puede compilar tu proyecto de manera estandarizada.

- Posibilidad de definir tareas extra: Limpieza de archivos temporales, generación de paquetes, ejecución de tests automáticos, etc.

¿Cómo funciona make internamente?

Make se basa en la lógica de dependencias y objetivos: cada «objetivo» del Makefile tiene asociadas unas «dependencias» (archivos de los que depende para construirse) y unas recetas (los comandos a ejecutar, siempre indentados con tabulación). Cuando ejecutas «make objetivo», el programa analiza si ese objetivo ya existe y si está actualizado respecto a sus dependencias. Si alguna dependencia es más reciente que el objetivo, ejecuta la receta asociada para reconstruirlo.

La sintaxis básica sería:

objetivo: dependencias

comando1

comando2

Por ejemplo, para compilar un ejecutable llamado main a partir de los archivos main.c y util.o:

main: main.c util.o

gcc -o main main.c util.o

Como ves, el objetivo es main, y depende de main.c y util.o. Si alguno de estos archivos cambia, make ejecutará la receta justo debajo (el comando gcc).

Primeros pasos: compilación básica sin Makefile

Antes de introducirnos a fondo en la creación de Makefile, vamos a ver cómo se compila tradicionalmente un programa sencillo. Supón que tienes este archivo en C:

#include <stdio.h>

int main() {

printf("Hola mundo\n");

return 0;

}

Para compilarlo manualmente:

gcc hola.c -o hola

Perfecto, ya tienes tu ejecutable hola. Sin embargo, si modificas el fichero fuente deberás volver a ejecutar este comando entero cada vez. Y si tu proyecto crece, las líneas se harán cada vez más largas y difíciles de recordar.

Compilando con make: la magia de las reglas implícitas y automáticas

La herramienta make es tan inteligente que, incluso sin un Makefile explícito, puede compilar programas sencillos a partir de sus convenciones internas. Por ejemplo, si tienes hola.c en tu carpeta y ejecutas:

make hola

Make detecta la presencia del fichero y, mediante sus reglas implícitas, utiliza el compilador adecuado para generar el binario hola a partir del fuente hola.c. Si el ejecutable ya está creado y es más reciente que el fuente, no hace nada. Si borras el ejecutable y vuelves a ejecutar make hola, volverá a compilarlo sin que necesites recordar los parámetros.

¿Por qué es esencial un Makefile en proyectos reales?

La magia de las reglas internas de make se agota rápidamente en cuanto el proyecto empieza a tener varios ficheros fuente, cabeceras y dependencias cruzadas. En ese caso, make por sí solo no sabrá qué incluir, con qué opciones de compilador trabajar ni cómo enlazar los objetos. Ahí es donde el Makefile se convierte en tu mejor aliado, ya que le dice a make cómo debe tratar cada archivo, cómo compilar los objetos individuales y cómo enlazarlos para producir uno o más ejecutables.

La estructura del Makefile: teoría y práctica

Un Makefile tradicional consta de una o varias reglas formadas por tres partes: el objetivo, sus dependencias y una receta de comandos. Las líneas de los comandos que se ejecutan deben empezar (sí o sí) con una tabulación, nunca espacios. De lo contrario, make dará error.

objetivo: dependencias

comando1

comando2

...

Explicación de los términos:

- Objetivo: Suele ser el nombre del ejecutable, un archivo objeto o incluso una acción interna como «clean».

- Dependencias: Archivos que deben existir y estar actualizados para que el objetivo se pueda crear. Si alguna dependencia es más nueva que el objetivo, make ejecuta la receta.

- Comandos: Las instrucciones de compilación, borrado, empaquetado, etc. Deben ir indentadas con tabulador.

Ejemplo muy básico de Makefile para compilar dos archivos fuente y generar un ejecutable:

test: test.o main.o

gcc -o test test.o main.o

test.o: test.c

gcc -o test.o -c test.c

main.o: main.c test.h

gcc -o main.o -c main.c

Así, si haces make, primero comprobará si existen los objetos; si no, los compilará, y luego los enlazará en el ejecutable test.

Repasando los conceptos clave según el flujo de trabajo real

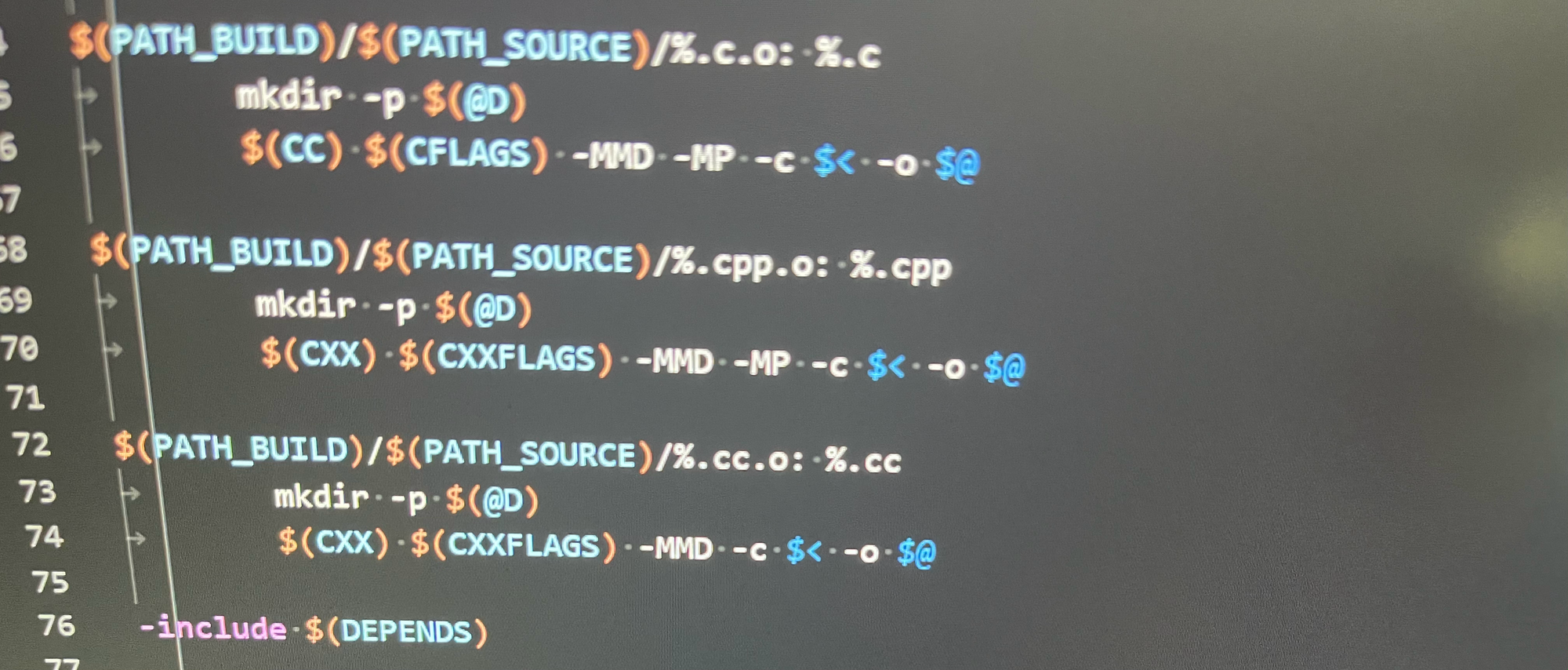

A medida que tu proyecto se complica, es fundamental entender cómo organizar las dependencias, los objetos y las reglas para que make recompile sólo lo necesario. Por ejemplo, si modificas sólo un archivo .h, querrás asegurarte de que todos los .c que lo incluyan se recompilen, pero nada más.

Supón que tienes el siguiente conjunto de archivos:

- principal.c: el programa principal, incluye hola.h

- hola.c: funciones auxiliares

- hola.h: cabecera de funciones

Un Makefile simple pero funcional sería:

hola: principal.o hola.o

gcc -o hola principal.o hola.o

principal.o: principal.c hola.h

gcc -c principal.c

hola.o: hola.c hola.h

gcc -c hola.c

Ahora cada cosa depende de lo que toca, y sólo se recompila lo que ha cambiado o depende de lo que ha cambiado.

Variables en Makefile: reutiliza y simplifica

Una de las armas más potentes de los Makefile son las variables. Con ellas puedes definir, por ejemplo, el compilador, las flags usuales, el nombre del binario, los objetos, etc. Así sólo necesitas cambiar algo en una línea y el resto del Makefile se actualiza solo.

Ejemplo típico:

CC=gcc

CFLAGS=-I.

OBJ=principal.o hola.o

hola: $(OBJ)

$(CC) -o hola $(OBJ) $(CFLAGS)

%.o: %.c hola.h

$(CC) -c -o $@ $< $(CFLAGS)

Aquí:

- $(CC) es la variable del compilador.

- $(CFLAGS) son las opciones que se pasan al compilador.

- $(OBJ) contiene la lista de objetos.

- $@ se sustituye por el nombre del objetivo, y $< por la primera dependencia.

Esto te permite generar reglas mucho más generales y flexibles. Por ejemplo, si añades otro .o sólo tendrás que modificar la variable OBJ.

Recomendación: usa variables para evitar repeticiones y facilitar cambios

Definir variables al inicio del Makefile es una práctica clave para la mantenibilidad y legibilidad del proyecto. Puedes definir desde el nombre del ejecutable hasta los directorios de cabeceras, objetos y fuentes:

CC=gcc

CFLAGS=-Wall -g -I./include

OBJ=main.o func.o utils.o

mi_programa: $(OBJ)

$(CC) -o $@ $^ $(CFLAGS)

$^ representa todas las dependencias (en este caso, los objetos). Así, sólo hay que tocar la variable OBJ para modificar la lista de fuentes.

Añadiendo reglas especiales: all, clean y otras tareas útiles

En la mayoría de proyectos, necesitas tareas extra además de la compilación. Por ejemplo:

- Limpieza de archivos intermedios (.o) y binarios (clean).

- Construcción de todos los binarios de una tacada (all).

- Generación de paquetes, documentación, tests, etc.

Ejemplo de Makefile con all y clean:

CC=gcc

CFLAGS=-I.

OBJ=principal.o hola.o

todo: hola

hola: $(OBJ)

$(CC) -o hola $(OBJ) $(CFLAGS)

%.o: %.c hola.h

$(CC) -c -o $@ $< $(CFLAGS)

clean:

rm -f hola *.o

Ahora, si ejecutas make o make todo, se compilará el binario. Si ejecutas make clean, se eliminan los binarios y los archivos objeto.

Importante: Si tienes un archivo en el directorio llamado «clean», make no ejecutará la receta al usar «make clean» a menos que declares el objetivo como .PHONY:

.PHONY: clean

clean:

rm -f hola *.o

Optimización y mantenimiento de dependencias: incluye los .h correctamente

Uno de los errores más frecuentes de los principiantes es no declarar las dependencias hacia los archivos .h, lo que puede llevar a que, al modificar una cabecera, los fuentes que la incluyen no se recompilen.

Para solucionarlo, declara explícitamente la dependencia de cada objeto a su(s) correspondiente(s) .h. O bien, usa reglas automáticas:

%.o: %.c hola.h

$(CC) -c -o $@ $< $(CFLAGS)

Así, cada vez que hola.h cambia, make recompila los objetos dependientes.

Automatización avanzada de dependencias: makedepend y alternativas

Para proyectos grandes, gestionar a mano las dependencias puede ser muy pesado, sobre todo si unos .h incluyen a otros. Aquí entran en juego herramientas como makedepend, pensadas para generarlas automáticamente y mantener el Makefile actualizado. Para gestionar casos más complejos, especialmente cuando se trabaja en plataformas multiplataforma, puede ser útil entender eficiente y flexible.

- Ejecuta:

makedepend -I./include *.c

- Esto agregará al Makefile las líneas de dependencias correctas al final.

Estructura típica de un Makefile profesional

CFLAGS=-I./include

OBJETOS=main.o utils.o func.o

FUENTES=main.c utils.c func.c

programa: $(OBJETOS)

gcc $(OBJETOS) -o programa

depend:

makedepend $(CFLAGS) $(FUENTES)

clean:

rm -f programa *.o

Makefile para proyectos distribuidos en varios directorios

Cuando el número de directorios crece (por ejemplo, con varios módulos y librerías), lo normal es tener un Makefile principal que delega en otros Makefile secundarios. Por ejemplo, puedes tener un Makefile en el directorio raíz que llama a los Makefile de cada módulo con:

module1:

make -C module1

module2:

make -C module2

Y luego el enlace final de todos los .o o librerías generadas en cada carpeta.

Integrando Makefile en entornos no Unix: Visual Studio y NMAKE

Si trabajas en Windows, Visual Studio ofrece soporte para proyectos basados en Makefile mediante la herramienta NMAKE o la opción de «Proyectos de archivo Make». Puedes crear un proyecto desde la plantilla de Makefile, especificar tus comandos de compilación, limpieza y salida desde el asistente y trabajar integrando tu Makefile dentro del IDE, beneficiándote de herramientas como IntelliSense y depuración avanzada.

En Visual Studio 2017 en adelante:

- Elige «Archivo > Nuevo > Proyecto», busca «Makefile», selecciona la plantilla y define los comandos para compilar, limpiar y depurar.

- En la pestaña de propiedades del proyecto puedes configurar rutas, comandos y opciones.

- Para obtener una mejor integración, consulta el tutorial sobre cómo gestionar errores en Windows.

Alternativas modernas a Makefile: CMake y más

Aunque Makefile sigue siendo el estándar de hecho en entornos Unix, otros sistemas como CMake han ganado mucha popularidad, sobre todo por su capacidad multiplataforma y su sintaxis más manejable para proyectos muy grandes. Para una guía práctica, puede ser útil saber en combinación con CMake.

CMake genera los Makefile por ti a partir de una descripción de alto nivel. Para un proyecto sencillo, basta un fichero CMakeLists.txt así:

cmake_minimum_required(VERSION 2.8) project(Hola) add_executable(hola main.c hola.c)

Después ejecuta «cmake .» para generar los Makefile y «make» para compilar. También puedes crear un subdirectorio build, ejecutar cmake .. desde allí y luego make para mantener el proyecto organizado y escalable.

Buenas prácticas y consejos clave para Makefile

- Cuida los tabuladores: Los comandos de las recetas siempre deben empezar con tabulador, no con espacios.

- Declara correctamente todas las dependencias, incluidos los .h: Así evitarás recompilaciones indebidas y errores por código desactualizado.

- Usa variables para los nombres de ejecutables, directorios y flags: Facilita la modificación y reduce errores.

- Incluye objetivos como clean, all, depend: Así tu proyecto será más fácil de usar y mantener.

- Para proyectos grandes, considera usar makedepend o CMake: Así automatizas la gestión de dependencias y escalas mejor.

- Apoya la limpieza de archivos temporales: No llenes el directorio de objetos inutilizados o binarios que pueden causar problemas a la hora de compartir el código.

- Haz que el primer objetivo sea el ejecutable principal o el objetivo «all»: Así cuando alguien escriba make sin argumentos, será esto lo que se compila.

- Agrega comentarios en el Makefile cuando sea apropiado: Aunque no son obligatorios, facilitan la comprensión para terceros (o para ti dentro de unas semanas).

Errores frecuentes y cómo evitarlos

- Confundir espacios y tabuladores al empezar las recetas de comandos.

- Olvidar declarar las dependencias hacia los archivos de cabecera (.h).

- No declarar un objetivo como .PHONY si no genera un archivo, lo que puede llevar a comportamientos extraños si existe un fichero o directorio con ese mismo nombre.

- No usar variables para los nombres y rutas, duplicando información y dificultando el mantenimiento.

- No limpiar los archivos temporales o binarios antes de nuevas compilaciones, lo que puede provocar errores confusos.

Personalizando tu Makefile para tareas complejas

Además de compilar y limpiar, puedes crear reglas personalizadas para:

- Empaquetar el código en un archivo ZIP o TAR.

- Lanzar automáticamente el ejecutable tras compilar.

- Generar documentación (por ejemplo, con Doxygen).

- Ejecutar tests automatizados y mostrar resultados.

- Preparar el código para distribución, copiando sólo los fuentes y archivos relevantes.

Por ejemplo, para generar un archivo comprimido:

dist:

zip mi_proyecto.zip *.c *.h Makefile README.md

Ejemplo integral de Makefile para un proyecto completo

CC=gcc

CFLAGS=-Wall -g -I.

DEPS=hola.h

OBJ=principal.o hola.o

%.o: %.c $(DEPS)

$(CC) -c -o $@ $< $(CFLAGS)

hola: $(OBJ)

$(CC) -o $@ $^ $(CFLAGS)

.PHONY: clean dist

clean:

rm -f hola *.o

Casos reales y recomendaciones finales

A lo largo de los años, make y Makefile siguen siendo imprescindibles para la compilación eficiente y organizada de proyectos en C, C++ y muchos otros lenguajes. Aunque existen alternativas modernas como CMake, aprender a dominar Makefile es una base que te ayudará en cualquier entorno de desarrollo serio.

Recuerda que cada proyecto puede requerir ajustes específicos en su Makefile. Lo más importante es entender la lógica de objetivos, dependencias y recetas, para luego aprovechar la potencia de make automatizando cualquier tarea necesaria. No dudes en estudiar los Makefile de otros proyectos, utilizar herramientas automáticas de gestión de dependencias y experimentar con objetivos adicionales.

Aplicar todo lo aprendido aquí te permitirá reducir errores humanos, ahorrar tiempo y facilitar a otros (o a ti mismo en el futuro) la tarea de compilar, mantener y distribuir tu software de manera profesional y eficiente, sea cual sea el tamaño del proyecto.

Redactor apasionado del mundo de los bytes y la tecnología en general. Me encanta compartir mis conocimientos a través de la escritura, y eso es lo que haré en este blog, mostrarte todo lo más interesante sobre gadgets, software, hardware, tendencias tecnológicas, y más. Mi objetivo es ayudarte a navegar por el mundo digital de forma sencilla y entretenida.