- Bezpieczeństwo bez zegara odnosi się do asynchronicznych projektów procesorów, w których zależność od globalnego zegara jest ograniczona lub całkowicie wyeliminowana.

- Nowoczesne procesory łączą w sobie pamięć podręczną, jednostki MMU, paralelizm i wiele wątków, co komplikuje zarówno wydajność, jak i bezpieczeństwo.

- Konstrukcje bez zegarów mogą łagodzić ataki związane z czasem, wymagają jednak nowych form monitorowania i audytu. sprzęt komputerowy.

- Wirtualizacja, wirtualne procesory (vCPU) i specjalistyczne akceleratory zwiększają powierzchnię ataku, dlatego niezbędna jest integracja zabezpieczeń na poziomie układu scalonego.

Ekspresja System bezpieczeństwa bez zegarka brzmi jak futurystyczna koncepcja.Ale w rzeczywistości jest to ściśle powiązane ze sposobem projektowania i zabezpieczania obecnych procesorów i systemów. Aby to właściwie zrozumieć, musimy zagłębić się w to, jak działa procesor, jak zorganizowane jest wykonywanie instrukcji i jaką rolę odgrywa słynny sygnał zegara w wyznaczaniu tempa działania całego systemu.

W ostatnich dekadach procesory ścigały się, aby zwiększyć swoją szybkość. częstotliwość zegara, zintegruj więcej tranzystorów i zwiększ ich paralelizmJednocześnie pojawiły się projekty mające na celu uniezależnienie się od zegara globalnego, zarówno w całym układzie scalonym, jak i w jego poszczególnych częściach. Ten obszar, czyli projekty asynchroniczne lub bez zegara, otwiera bardzo interesujące możliwości pod względem zużycia energii i odprowadzania ciepła… a także stawia czoła konkretnym wyzwaniom bezpieczeństwa, które często grupuje się pod pojęciem bezpieczeństwa bez zegara.

Procesor jako centrum systemu i jego związek z zegarem

Mówiąc o bezpieczeństwie zegarków, pierwszą rzeczą, o której należy pamiętać, jest to, czym jest procesor. Zasadniczo Jednostka centralna jest mózgiem komputera.:składnik, który interpretuje i wykonuje instrukcje programu, koordynuje pamięć, wejście/wyjście i specjalistyczne koprocesory, takie jak procesory GPU.

W nowoczesnym procesorze znajdujemy kilka odrębnych bloków. Z jednej strony jest jednostka arytmetyczna (ALU)Jednostka arytmetyczna (ALU) odpowiada za operacje matematyczne i logiczne na liczbach całkowitych. Następnie mamy rejestry, czyli małe, ultraszybkie pamięci, w których przechowywane są dane aktualnie przetwarzane przez procesor. A na dodatek, w każdym cyklu, znajduje się jednostka sterująca, która decyduje, co wykonać, co odczytać z pamięci i co zapisać.

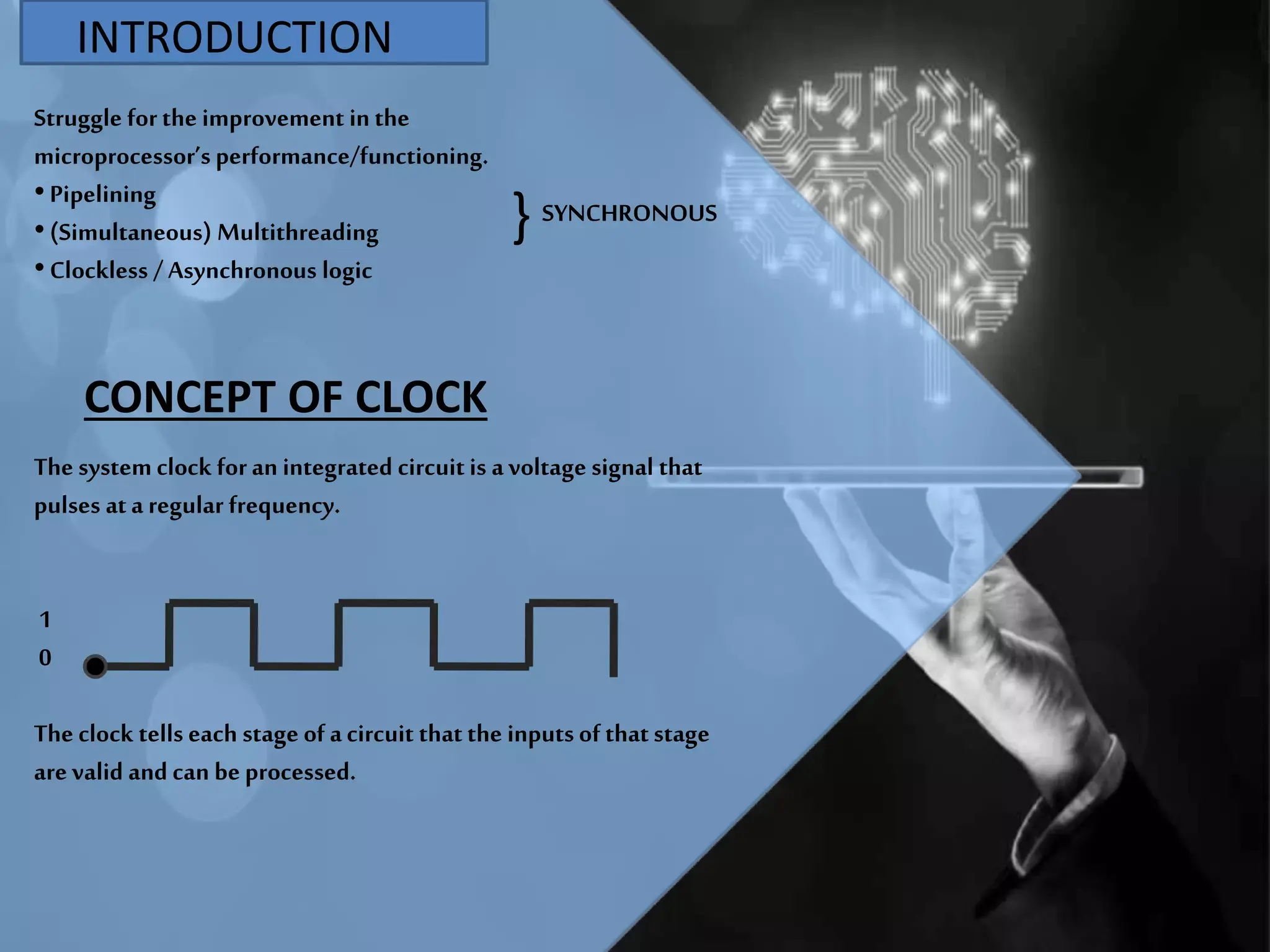

Większość współczesnych procesorów ma konstrukcję synchroniczną. Oznacza to, że wszystkie te wewnętrzne bloki są koordynowane za pomocą okresowy sygnał zegarowyRodzaj elektronicznego metronomu, który wyznacza tempo wykonywania instrukcji. Każde tyknie tego zegara przesuwa o jeden krok tzw. cyklu instrukcji: instrukcja jest pobierana, dekodowana, wykonywana, wyniki zapisywane, a cykl rozpoczyna się od nowa.

W tradycyjnym procesorze zegar jest generowany przez zewnętrzny oscylator, który wysyła miliony lub miliardy impulsów na sekundę. Częstotliwość tych impulsów, mierzona w hercach, megahercach lub gigahercach, informuje nas, ile „taktów” procesor ma do dyspozycji w każdej sekundzie na przesyłanie danych i wykonywanie operacji. Im wyższa częstotliwość zegara, tym większa potencjalna praca na sekundę.pod warunkiem, że reszta architektury będzie ją uzupełniać.

Wydajność zależy więc nie tylko od zegara, ale także od tego, ile instrukcji na cykl (IPC) Jest w stanie uzupełnić możliwości procesora. Iloczyn częstotliwości i IPC daje nam pojęcie o milionach instrukcji na sekundę, które może wykonać, chociaż teoretyczne dane są zazwyczaj znacznie bardziej optymistyczne niż te obserwowane w rzeczywistych programach.

Od stałego okablowania do zintegrowanych mikroprocesorów

Aby umieścić projekty bez zegara w odpowiednim kontekście, warto przyjrzeć się ewolucji procesora. Wczesne komputery elektroniczne, takie jak ENIAC, były przewodowe maszyny o stałym programieAby zmienić zadania, system musiał zostać fizycznie przebudowany. Rewolucyjnym pomysłem był komputer z zapisanym programem, w którym instrukcje znajdują się w pamięci; procesor po prostu je odczytuje i wykonuje.

Architektura programów przechowywanych, kojarzona z Johnem von Neumannem, ostatecznie zwyciężyła. Instrukcje i dane współdzielą tę samą przestrzeń pamięciW przeciwieństwie do architektury harwardzkiej, która fizycznie oddziela oba typy informacji, obecnie niemal wszystkie procesory ogólnego przeznaczenia korzystają z architektury von Neumanna, chociaż w świecie systemów wbudowanych nadal istnieje wiele czystych lub hybrydowych procesorów harwardzkich.

Pierwsze procesory budowano z przekaźników lub lamp próżniowych. Były nieporęczne, powolne i miały niezawodność bardzo ograniczone. Przejście do tranzystorów półprzewodnikowych w latach 50. i 60. XX wieku umożliwiło radykalnie zwiększyć prędkość i zmniejszyć zużycie i rozmiarNastępnie nastąpiło przejście od układów dyskretnych do układów scalonych (IC), co oznaczało umieszczanie coraz większej liczby tranzystorów na jednym chipie.

Wraz z pojawieniem się układów scalonych, najpierw małej skali (SSI), następnie średniej skali (MSI), dużej skali (LSI), a na końcu bardzo dużej skali (VLSI), procesor był kompresowany do momentu, aż zmieścił się w wszystko na jednym lub kilku chipachIntegracja ta osiągnęła punkt kulminacyjny w mikroprocesorze, w którym cała jednostka przetwarzająca jest wytwarzana na pojedynczym krzemowym chipie.

El Intel 4004Procesor Intel 8080, wprowadzony na rynek w 1971 roku, był jednym z pierwszych komercyjnych mikroprocesorów. Wkrótce pojawiły się mocniejsze konstrukcje, takie jak Intel 8080, który stał się podstawą komputerów osobistych. Od tego momentu termin CPU był niemal zawsze używany w odniesieniu do tych mikroprocesorów.

Kluczowe wewnętrzne komponenty nowoczesnego procesora

Nowoczesne procesory poświęcają znaczną część powierzchni krzemu na elementy pomocnicze przeznaczone do aby maksymalnie wykorzystać każdy cykl zegaraNa przykład niemal każdy procesor zawiera kilka poziomów pamięci podręcznej: są to małe, ale bardzo szybkie pamięci zlokalizowane w pobliżu rdzeni, które przechowują kopie najczęściej używanych danych, dzięki czemu nie muszą stale uzyskiwać dostępu do pamięci RAM.

Oprócz pamięci podręcznej L1, L2 i często L3, złożony procesor zawiera jednostka zarządzania pamięcią (MMU) który tłumaczy adresy wirtualne (obsługiwane przez system operacyjny) na adresy fizyczne w pamięci RAM, zarządza pamięć wirtualna i zapewnia izolację pomiędzy procesami.

Na płaszczyźnie obliczeniowej mamy kilka wyspecjalizowanych jednostek wykonawczych: ALU dla liczb całkowitych, jednostka zmiennoprzecinkowa (FPU) W przypadku operacji dziesiętnych do szybkiego obliczania lokalizacji pamięci stosuje się jednostki generowania adresów (AGU), a w wielu architekturach do jednoczesnego wykonywania operacji na wielu punktach danych stosuje się jednostki wektorowe lub SIMD.

Istnieje również jednostka sterująca, która może być oparta na logice przewodowej lub mikrokodzie, czyli wewnętrzny program, który tłumaczy każdą instrukcję wysokiego poziomu w sekwencji wewnętrznych sygnałów sterujących. W wielu procesorach ten mikrokod można aktualizować, co pozwala na korektę błędów projektowych lub dostosowanie działania po fakcie.

Na koniec mamy baterię rejestrów wewnętrznych: rejestry ogólnego przeznaczenia, akumulatory, liczniki programów, rejestry stanu z flagami wskazującymi na przykład, czy wynik operacji jest zerowy, ujemny, czy też spowodował przepełnienie itd. Wszystko to jest koordynowane zgodnie z klasyczną pętlą. przechwytywanie, dekodowanie i wykonywanie instrukcji.

Jak uruchomić program krok po kroku

Podstawowa operacja każdego procesora sprowadza się do pobierania instrukcji z pamięci i przetwarzania ich jedna po drugiej. Odbywa się to w trzech głównych fazach. Po pierwsze, etap przechwytywanie (pobieranie), w którym instrukcja, której adresowanie podaje licznik programu, jest odczytywana z pamięci.

Następnie następuje faza dekodowania. Nowo przechwycona instrukcja przechodzi przez dekoder binarny, który analizuje jej kod operacji (kod operacji) i tłumaczy ten wzór bitowy na konkretne sygnały które włączają lub wyłączają części procesora. To właśnie tam decyduje się, czy jest to dodawanie, skok, ładowanie z pamięci itd., i które rejestry lub adresy są zaangażowane.

Na koniec wykonywana jest operacja. Jednostka ALU lub odpowiadająca jej jednostka wykonuje obliczenia lub ruch danych, a wynik jest zazwyczaj zapisywany w rejestrze lub pamięci. Jeśli przebieg programu wymaga zmiany, na przykład poprzez skok warunkowy, licznik programu jest aktualizowany o nowy adres. Ten zestaw instrukcje, dane i skoki To właśnie ona odpowiada za tworzenie pętli, funkcji, warunków i całej logiki naszych programów.

W prostych procesorach wszystko dzieje się liniowo i sekwencyjnie. Ale w nowoczesnych procesorach Wiele z tych etapów nakłada się na siebie, wykorzystując techniki paralelizmuCelem jest, aby w każdym cyklu zegara wykonywano jak najwięcej pracy i aby sprzęt nie pozostawał bezczynny.

Paralelizm, kanałowanie i wykonywanie poza kolejnością

Aby uniknąć marnowania zegarka, projektanci wprowadzili rurociągiŚcieżka danych jest podzielona na kilka etapów, podobnie jak linia montażowa. Podczas gdy jedna instrukcja jest dekodowana, kolejna jest już pobierana z pamięci, a kolejna może być wykonywana w jednostce ALU.

Problem polega na tym, że czasami jedna instrukcja wymaga wyniku innej, która jeszcze się nie zakończyła. To tworzy zależności danych i wymusza wprowadzanie bąbelków lub czekanie w potoku. Aby zminimalizować te opóźnienia, stosuje się techniki takie jak przekazywanie operandów, przewidywanie rozgałęzień i późniejsze. wykonywanie poza kolejnością, w którym procesor wewnętrznie zmienia kolejność instrukcji, pod warunkiem, że końcowy wynik programu jest respektowany.

Następnym krokiem było zastosowanie konstrukcji superskalarnej: wyposażenie procesora w kilka jednostek wykonawczych tego samego typu, aby móc wydawać wiele instrukcji na cykl zegarapod warunkiem, że nie ma między nimi konfliktów. Wewnętrzny dyspozytor analizuje przepływ instrukcji, wykrywa, które z nich można wykonać równolegle, i rozdziela je między poszczególne jednostki.

Wszystkie te Tricks Zaliczają się do tzw. paralelizm instruktażowy (ILP)Praktyczne ograniczenia tych technik i coraz większe trudności w dalszym zwiększaniu częstotliwości taktowania bez znaczącego zwiększenia zużycia energii i wydzielanego ciepła sprawiły, że w pewnym momencie producenci zaczęli inwestować w... paralelizm na poziomie zadań:wiele wątków i wiele rdzeni na chip (oraz mechanizmy takie jak parking dla rdzeni).

Tak się rodzą procesory wielordzeniowe oraz architektury z wielowątkowością sprzętową, w których każdy rdzeń może utrzymywać stan kilku wątków wykonywania i szybko przełączać się między nimi, aby lepiej wykorzystać zasoby wewnętrzne, podczas gdy inne wątki czekają na dane z pamięci.

Rola częstotliwości zegara i jej ograniczenia fizyczne

Wracając do zegara, ważne jest, aby zauważyć, że sygnał, który synchronizuje procesor, jest ostatecznie sygnał elektryczny, który rozprzestrzenia się przez układ scalonyWraz ze wzrostem częstotliwości i liczby tranzystorów, utrzymanie idealnej synchronizacji sygnału staje się bardzo trudne. Pojawiają się problemy z rozkładem sygnału taktującego, przesunięciami fazowymi i integralnością sygnału.

Z drugiej strony, każda zmiana taktu powoduje zmianę stanu wielu tranzystorów, nawet jeśli dany obszar procesora nie wykonuje w danym momencie żadnej użytecznej czynności. To przekłada się na zużycie energii i rozpraszanie ciepła Aby temu zaradzić, wprowadzono techniki takie jak bramkowanie zegara, które selektywnie wyłącza sygnał zegara w nieużywanych blokach, zmniejszając w ten sposób zużycie energii.

Jednak po przekroczeniu pewnego progu zwiększanie częstotliwości przestaje być rozsądne: problemy ze zużyciem energii, temperaturą i rozkładem częstotliwości taktowania gwałtownie rosną. To wąskie gardło To jeden z powodów, dla których rozważano koncepcję całkowitego lub częściowego zrezygnowania z zegara globalnego: tutaj właśnie wchodzą w grę projekty asynchroniczne lub „bezzegarowe”.

W projekcie asynchronicznym zamiast pojedynczego zegara oznaczającego El Tiempo dla całego układu, To właśnie dane i sygnały sterujące synchronizują operacjeBloki komunikują się za pomocą protokołów żądań i potwierdzeń (uzgadniania): gdy dane są gotowe, producent powiadamia o tym konsumenta, a konsument reaguje bez czekania na ustalony sygnał zegara.

Zostały zbudowane w pełni asynchroniczne procesory Kompatybilny ze znanymi zestawami instrukcji, takimi jak rodzina AMULET oparta na architekturze ARM lub projekty oparte na architekturze MIPS. Istnieją również projekty hybrydowe, w których tylko niektóre jednostki (na przykład konkretna jednostka ALU) działają bez zegara globalnego, podczas gdy reszta procesora pozostaje synchroniczna.

Co rozumiemy pod pojęciem bezpieczeństwa bezobsługowego?

Mówiąc o bezpieczeństwie bez zegara, mieszają się dwie idee: z jednej strony projekt asynchroniczny, technika zmniejszająca zużycie i ciepłoZ drugiej strony, istnieje potrzeba zrezygnowania z zegara podczas analizowania, monitorowania i ochrony działania systemu przed atakami lub awariami.

W systemach synchronicznych wiele narzędzi bezpieczeństwa i monitorowania opiera się na istnieniu stabilny i przewidywalny rytm czasowyStosunkowo łatwo jest liczyć cykle, mierzyć czas trwania określonej operacji lub wykrywać nietypowe zachowania, mierząc odchylenia w czasach, które powinny być stałe.

W systemie asynchronicznym lub częściowo bez zegara te sztywne odniesienia czasowe ulegają rozmyciu. Czas wykonania operacji może zależeć od faktycznej dostępności danych, przeciążenia niektórych tras wewnętrznych lub drobnych odchyleń fizycznych. Z perspektywy atakującego może to utrudniać… trudniej jest przeprowadzać ataki typu side-channel oparte na czasieponieważ globalny zegar, który służy jako wspólny punkt odniesienia, znika.

Jednak ta sama dynamiczna natura komplikuje również sytuację każdemu, kto chce obserwować i audytować system od wewnątrz. Wiele sond i liczników sprzętowych jest zaprojektowanych do działania w oparciu o cykle zegara; bez wyraźnego zegara globalnego, mierz wydajność i wykrywaj podejrzane działania W takim przypadku wymagane są inne wskaźniki i mechanizmy.

Co więcej, asynchroniczna konstrukcja, dzięki uwolnieniu od zegara, umożliwia aktywację ścieżek danych w nieco innych momentach podczas każdego wykonania, co potencjalnie losowo wykrywa tymczasowe przecieki Może to jednak otworzyć także inne drzwi, na przykład w postaci innych i bardziej złożonych wzorców zużycia energii, które można wykorzystać w atakach polegających na analizie zużycia energii.

Reprezentacja danych, rozmiar słowa i bezpieczeństwo

Kolejnym ważnym czynnikiem związanym z architekturą procesora jest sposób, w jaki reprezentuje on i przetwarza dane. Prawie wszystkie współczesne procesory korzystają z reprezentacja binarna, przy czym wartości napięcia odpowiadają 0 i 1. Rozmiar słowa (8, 16, 32, 64 bity…) określa zakres liczb całkowitych, które mogą być obsługiwane bezpośrednio, oraz ilość adresowalnej pamięci.

Z punktu widzenia bezpieczeństwa rozmiar słowa wpływa na przestrzeń adresową i prawdopodobieństwo kolizje, przepełnienia i błędy wskaźnikówSystem 32-bitowy z 2^32 możliwymi adresami ma bardzo wyraźne ograniczenia w porównaniu z systemem 64-bitowym. Co więcej, wiele współczesnych mechanizmów ochrony, takich jak niektóre rozszerzenia pamięci chronionej, opiera się na dużej przestrzeni adresowej.

Użycie MMU i translacji adresów wprowadza również dodatkową warstwę pomiędzy programem a pamięcią fizyczną, co jest kluczowe dla izolowanie procesówZaimplementuj pamięć wirtualną i chroń jądro. W kontekstach asynchronicznych koordynacja między tymi tłumaczeniami a sygnałami ręcznymi między blokami bez zegara musi być bardzo dobrze zaprojektowana, aby uniknąć luk w zabezpieczeniach lub sytuacji wyścigu.

Z kolei rozszerzenia wektorowe (SIMD) i jednostki zmiennoprzecinkowe umożliwiają równoległą pracę z dużymi wolumenami danych. To miecz obosieczny: z jednej strony, Przyspiesza algorytmy kryptograficzne i zadania analityczne.Z drugiej strony, jeśli zostanie wykorzystana w sposób złośliwy, zapewnia dużą moc obliczeniową do łamania słabych szyfrów lub przeprowadzania ataków siłowych.

W scenariuszu bez zegara lub częściowo asynchronicznym sposób programowania i ochrony tych równoległych jednostek obliczeniowych musi uwzględniać, że Wzory realizacji i konsumpcji nie podlegają już stałemu rytmowi narzucanemu przez zegar.ale będzie reagować na rzeczywistą dynamikę danych, co także wpływa na projektowanie przeciwdziałań kanałom bocznym.

Masowy paralelizm, wielowątkowość i wektory: wpływ na bezpieczeństwo bez zegara

Nowoczesne procesory dążą do zwiększenia wydajności nie tylko poprzez podniesienie częstotliwości taktowania, ale także poprzez wykonywanie większej ilości zadań równolegle. Wymaga to wielu rdzeni, sprzętowej wielowątkowości i… jednostki wektorowe zdolne do przetwarzania wielu punktów danych na instrukcjęDo tego wszystkiego dochodzi wzrost znaczenia konkretnych akceleratorów, takich jak GPU, DSP czy TPU.

Z perspektywy bezpieczeństwa, każdy nowy blok wykonawczy i każdy nowy poziom paralelizmu to dodatkowa powierzchnia do ochrony. Koordynacja jest konieczna. spójność pamięci podręcznej, zarządzanie pamięcią współdzieloną, mechanizmy wzajemnego wykluczania i unikania sytuacji wyścigu oraz wycieków informacji pomiędzy wątkami lub procesami współbieżnymi.

W środowiskach bez zegara lub hybrydowych koordynacja ta opiera się bardziej na protokołach komunikacji między blokami niż na globalnych cyklach zegara. Na przykład jądro może używać sygnały żądania i rozpoznania aby uzyskać dostęp do pamięci lub zasobu współdzielonego, a efektywne opóźnienie będzie zależało od rzeczywistego ruchu w tym momencie, a nie od ustalonej liczby cykli.

To zachowanie, patrząc z zewnątrz, utrudnia przeprowadzenie niektórych ataków, które opierają się na bardzo precyzyjnych pomiarach czasu, opartych na liczbie cykli zegara. Jednocześnie projektanci systemów bezpieczeństwa muszą wyjść poza zliczanie cykli i polegać na... liczniki zdarzeń, pomiar ruchu, zużycie energii i inne oznaki pozwalające wykryć podejrzane zachowanie.

Właśnie dlatego wielu producentów integruje liczniki wydajności sprzętowej, które umożliwiają monitorowanie w czasie rzeczywistym takich rzeczy, jak braki w pamięci podręcznej, przewidywania nieudanych rozgałęzień, dostęp do określonych pamięci itp. Prawidłowo używane liczniki te stanowią potężne narzędzie zarówno do optymalizacji wydajności, jak i... znaleźć anomalie wzorców charakterystyczny dla malware lub zaawansowanych exploitów, nawet w architekturach częściowo asynchronicznych.

Wirtualizacja, vCPU i izolacja w nowoczesnych środowiskach

Kolejnym kluczowym elementem dzisiejszego krajobrazu jest wirtualizacja. W chmurze stale pracujemy z Procesory wirtualne (vCPU), które są logicznymi fragmentami mocy obliczeniowej przydzielonej do maszyny wirtualne lub kontenerów umieszczonych na współdzielonym sprzęcie fizycznym.

Każdy wirtualny procesor (vCPU) to w zasadzie zestaw wątków lub czasów wykonania, które hiperwizor planuje na rdzeniach fizycznych. Aby to działało prawidłowo, fizyczny procesor oferuje specjalne tryby uprzywilejowane które umożliwiają hiperwizorom tworzenie i izolowanie maszyny wirtualne, przechwytywać pewne poufne instrukcje i zarządzać pamięcią każdego gościa bez możliwości ingerencji lub szpiegowania innych.

W tym kontekście bezpieczeństwo bez zegara oznacza, że przydział czasu procesora pomiędzy maszynami wirtualnymi zależy nie tylko od jednolitego zegara, ale także od bardziej dynamiczne mechanizmy planowania obsługiwane przez sprzęt. Hiperwizor nadal widzi cykle zegara, ale sposób, w jaki te cykle są przekształcane w efektywną pracę na każdym rdzeniu, może zostać zmieniony przez wewnętrzne bloki asynchroniczne.

Z punktu widzenia bezpieczeństwa oznacza to konieczność zaprojektowania narzędzi monitorujących, które nie tylko liczą cykle, ale także potrafią interpretować liczniki wydajności, statystyki wykorzystania i zdarzenia niskiego poziomu. wykrywać nadużycia zasobów, ucieczki maszyn wirtualnych lub nieregularne wzorce co wskazuje na włamanie.

Co więcej, w środowiskach wymagających dużej mocy obliczeniowej, w których w pełni wykorzystywane są jednostki wektorowe, procesory GPU i inne akceleratory, menedżerowie ds. bezpieczeństwa muszą wziąć pod uwagę, że bloki te, niezależnie od tego, czy są synchroniczne, czy asynchroniczne, mogą stać się narzędziami przyspieszyć ataki kryptograficzne, wydobywanie kryptowalut za plecami użytkownika lub przeprowadzać analizę dużych ilości skradzionych danych.

Wydajność, zużycie energii i podkręcanie w porównaniu z konstrukcją bez zegara

Na koniec musimy rozważyć związek między wydajnością a zużyciem energii. Zwiększenie częstotliwości taktowania poprzez podkręcanie (np. poprzez wykonanie Test stabilności z OCCT) pozwala procesorowi wykonywać więcej operacji na sekundęJednak znacznie zwiększa to zużycie energii i temperaturę. W rzeczywistości wiele obecnych procesorów dynamicznie dostosowuje częstotliwość i napięcie w zależności od obciążenia i temperatury wewnętrznej.

Projekty asynchroniczne oferują alternatywę: zamiast używać bardzo szybkiego zegara i starać się, aby wszystko było w fazie, Umożliwiają każdemu blokowi funkcjonowanie w tempie narzuconym przez dane.W okresach niskiego obciążenia nieaktywne elementy praktycznie nie zmieniają swojego stanu, co pozwala ograniczyć zużycie energii bez konieczności stosowania skomplikowanych mechanizmów zarządzania energią opartych na zegarze.

Z punktu widzenia bezpieczeństwa mniejsze zużycie i mniejsze ciepło to nie tylko kwestia środowiska czy rachunków za prąd. Oznacza to również mniejsze obciążenie podzespołówmniejsze prawdopodobieństwo awarii wywołanych elektromigracją lub upływem prądu oraz potencjalnie mniejsze narażenie na ataki mające na celu wykorzystanie zachowania systemu w ekstremalnych warunkach temperaturowych lub napięciowych.

Zaprojektowanie w pełni asynchronicznego i bezpiecznego systemu nie jest jednak trywialne. Wymaga bardzo rygorystycznej weryfikacji protokołów komunikacyjnych między blokami, warunków wyścigu i stanów pośrednich, aby zapobiec błędom. zachowania niedeterministyczne, które mogą zostać wykorzystane przez atakującegoZłożoność projektu, niedobór dopracowanych narzędzi i konieczność zapewnienia wstecznej kompatybilności z istniejącym oprogramowaniem sprawiły, że na razie większość komercyjnych procesorów działa głównie synchronicznie, tworząc małe asynchroniczne wyspy.

Połączenie wszystkich tych czynników – architektury wewnętrznej, zarządzania zegarem, paralelizmu, wirtualizacji i zasilania – sprawia, że bezpieczeństwo w środowiskach bez zegara globalnego wymaga zachowania delikatnej równowagi. Projekty asynchroniczne ograniczają niektóre ataki oparte na synchronizacji i ułatwiają stosowanie wysoce zaawansowanych strategii oszczędzania energii, ale jednocześnie stwarzają nowe wyzwania w zakresie monitorowania, audytu i weryfikacji działania sprzętu, dlatego kluczem jest integracja. solidne mechanizmy obserwacji i izolacji od samego krzemu aż po oprogramowanie najwyższej klasy.

Pisarz z pasją zajmujący się światem bajtów i technologii w ogóle. Uwielbiam dzielić się swoją wiedzą poprzez pisanie i właśnie to będę robić na tym blogu, pokazywać Ci wszystkie najciekawsze rzeczy o gadżetach, oprogramowaniu, sprzęcie, trendach technologicznych i nie tylko. Moim celem jest pomóc Ci poruszać się po cyfrowym świecie w prosty i zabawny sposób.