- クロックレス セキュリティは、グローバル クロックへの依存が軽減または排除される非同期 CPU 設計に関連します。

- 最新のプロセッサは、キャッシュ、MMU、並列処理、複数のスレッドを組み合わせているため、パフォーマンスとセキュリティの両方が複雑になっています。

- クロックレス設計はタイミング攻撃を軽減できますが、新しい形式の監視と監査が必要になります。 ハードウェア.

- 仮想化、vCPU、専用アクセラレータによって攻撃対象領域が拡大するため、シリコン レベルからセキュリティを統合することが不可欠になります。

式 時計のないセキュリティは未来的なコンセプトのように聞こえます。しかし、実際には、これは現在のプロセッサとシステムの設計と保護方法と密接に関連しています。これを正しく理解するには、CPUの内部動作、命令実行の構成、そして有名なクロック信号がシステム全体のペースを決める上でどのような役割を果たしているかを詳しく調べる必要があります。

ここ数十年、プロセッサは速度の向上に競争してきました。 クロック周波数、より多くのトランジスタを統合し、それらの並列性を高める同時に、チップ全体または特定の部分において、グローバルクロックへの依存からの脱却を試みる設計が登場しています。非同期設計、あるいはクロックレス設計というこの分野は、消費電力と放熱の面で非常に興味深い可能性を秘めています。そして同時に、クロックレスセキュリティという概念にまとめられることが多い、特定のセキュリティ課題も抱えています。

システムの中心となるCPUとクロックの関係

時計関連のセキュリティについて話すとき、まず最初に覚えておくべきことはCPUとは何かということです。基本的に、 中央処理装置はコンピューターの頭脳です。プログラム命令を解釈して実行し、メモリ、入出力、GPU などの特殊なコプロセッサを調整するコンポーネント。

現代のCPUには、いくつかの異なるブロックがあります。 算術論理ユニット(ALU)算術論理ユニット(ALU)は、整数を使った数学的および論理的演算を担当します。次に、プロセッサが現在処理中のデータが格納される、小型で超高速なメモリであるレジスタがあります。そして、これらすべてに加えて、サイクルごとに何を実行するか、メモリから何を読み取り、何を書き込むかを決定する制御ユニットがあります。

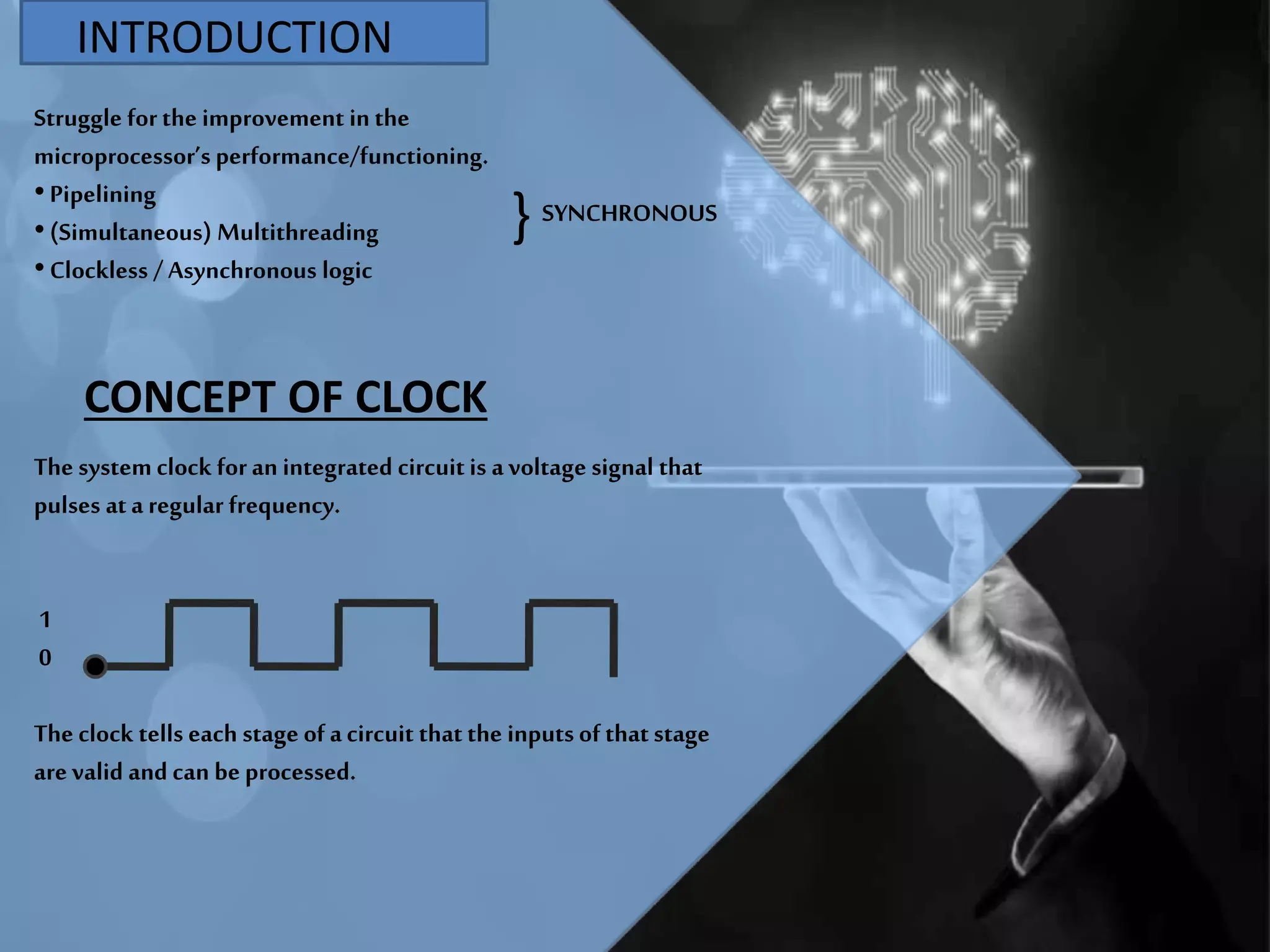

現代のプロセッサのほとんどは同期設計です。つまり、すべての内部ブロックは同期制御によって調整されます。 周期的なクロック信号実行のペースを決める一種の電子メトロノーム。このクロックの1ティックごとに、いわゆる命令サイクルが1ステップ進みます。命令はフェッチされ、デコードされ、実行され、結果が保存され、サイクルが再び始まります。

従来のプロセッサでは、クロックは毎秒数百万、数十億のパルスを送信する外部発振器によって生成されます。これらのパルスの周波数は、ヘルツ、メガヘルツ、ギガヘルツで測定され、CPUがデータの転送や演算処理に1秒間に使用できる「ティック」の数を示します。 クロック周波数が高くなるほど、1 秒あたりの潜在的な作業量が増えます。ただし、アーキテクチャの残りの部分がそれを補完するものとします。

したがって、パフォーマンスはクロックだけでなく、 サイクルあたりの命令数(IPC) プロセッサを完成させる能力です。周波数とIPCの積は、1秒間に何百万もの命令を実行できるかという目安となりますが、理論上の数値は通常、実際のプログラムで実際に見られる数値よりもはるかに楽観的です。

固定配線から統合マイクロプロセッサへ

クロックレス設計を理解するには、CPUの進化の過程を振り返ることが役立ちます。ENIACのような初期の電子計算機は 有線固定プログラムマシンタスクを変更するには、システムを物理的に配線し直す必要がありました。革命的なアイデアは、プログラム内蔵型コンピュータでした。プログラム内蔵型コンピュータでは、命令はメモリに常駐し、プロセッサはそれを読み込んで実行するだけです。

ジョン・フォン・ノイマンに関連するプログラム内蔵アーキテクチャは最終的に普及しました。その中で、 命令とデータは同じメモリ空間を共有する両方の種類の情報を物理的に分離するハーバード アーキテクチャとは異なり、今日ではほぼすべての汎用 CPU がフォン ノイマン アーキテクチャに従っていますが、組み込みの世界では多くの純粋またはハイブリッド ハーバード プロセッサが依然として存在しています。

最初のプロセッサはリレーや真空管で作られていました。それらは大きく、遅く、 信頼性 非常に限られていた。50年代と60年代の固体トランジスタへの飛躍により、 速度を大幅に向上し、消費量とサイズを削減そこから、個別回路から集積回路 (IC) への移行が行われ、1 つのチップ上にさらに多くのトランジスタが組み込まれるようになりました。

集積回路の登場により、最初は小規模(SSI)、次に中規模(MSI)、大規模(LSI)、そして最後に超大規模(VLSI)へとCPUは縮小され、 すべてを1つまたは数個のチップにこの統合により、処理ユニット全体が単一のシリコン チップ上に製造されるマイクロプロセッサが誕生しました。

El インテル 40041971年に発売されたIntel 8080は、最初の商用マイクロプロセッサの一つでした。その後すぐに、パーソナルコンピュータの基盤となるIntel 8080など、より強力な設計が登場しました。それ以降、「CPU」という用語は、これらのマイクロプロセッサを指すのにほぼ常に使用されるようになりました。

現代のCPUの主要な内部コンポーネント

現代のCPUは、シリコン表面の大部分を、次のような補助的な要素に割り当てています。 クロックサイクルを最大限に活用するたとえば、ほぼすべてのプロセッサには、複数レベルのキャッシュが組み込まれています。キャッシュとは、コアの近くに配置された小さいが非常に高速なメモリで、最もよく使用されるデータのコピーを保存し、RAM に頻繁にアクセスする必要がないようにするものです。

複雑なCPUには、L1、L2、そして多くの場合L3キャッシュに加えて、 メモリ管理ユニット(MMU) 仮想アドレス(オペレーティングシステムによって処理されるアドレス)をRAM内の物理アドレスに変換し、 仮想メモリ プロセス間の分離を実現します。

計算面には、整数用のALU、 浮動小数点ユニット(FPU) 10 進演算では、アドレス生成ユニット (AGU) を使用してメモリ位置をすばやく計算し、多くのアーキテクチャでは、ベクター ユニットまたは SIMD を使用して複数のデータ ポイントを同時に演算します。

また、ハードワイヤードロジックまたはマイクロコードベースの制御ユニットもあり、 各高水準命令を翻訳する内部プログラム 内部制御信号のシーケンス。多くのプロセッサでは、このマイクロコードを更新できるため、設計エラーの修正や事後的な動作調整が可能です。

最後に、汎用レジスタ、アキュムレータ、プログラム カウンタ、演算結果がゼロか負か、オーバーフローが発生したかなどを示すフラグ付きのステータス レジスタなど、一連の内部レジスタがあります。これらすべてが、従来のループに従って調整されます。 命令のキャプチャ、デコード、実行.

プログラムをステップバイステップで実行する方法

CPUの基本的な動作は、メモリから命令を取り出し、それを次々に処理することです。これは主に3つの段階で行われます。まず、 キャプチャ(フェッチ)プログラム カウンタによってアドレス指定される命令がメモリから読み取られます。

次にデコードフェーズが続きます。新しくキャプチャされた命令はバイナリデコーダを通過し、そこでオペレーションコード(オペコード)が検査され、 そのビットパターンを具体的な信号に変換する プロセッサの一部を有効または無効にする命令です。加算、ジャンプ、メモリからのロードなど、どのレジスタやアドレスが関係するかがここで決定されます。

最後に、演算が実行されます。ALUまたは対応するユニットが計算またはデータ移動を実行し、結果は通常レジスタまたはメモリに格納されます。条件付きジャンプなど、プログラムフローを変更する必要がある場合は、プログラムカウンタが新しいアドレスに更新されます。 命令、データ、ジャンプ 最終的にループ、関数、条件文、およびプログラムのすべてのロジックを形成するものになります。

単純なプロセッサでは、すべてが線形かつ連続的に実行されます。しかし、現代のCPUでは これらの段階の多くは並列処理技術を使用して重複しています目標は、各クロック サイクルで可能な限り多くの作業を実行し、ハードウェアがアイドル状態にならないようにすることです。

並列処理、チャネリング、アウトオブオーダー実行

時計を無駄にしないために、デザイナーは パイプラインデータパスは、組立ラインのように複数の段階に分かれています。ある命令がデコードされている間にも、次の命令は既にメモリからフェッチされており、さらに別の命令がALUで実行されている場合もあります。

問題は、ある命令がまだ完了していない別の命令の結果を必要とする場合があることです。これによりデータ依存関係が生じ、パイプラインにバブルや待機が発生します。これらの遅延を最小限に抑えるために、オペランド転送、分岐予測、そして後には アウトオブオーダー実行プログラムの最終結果が尊重される限り、プロセッサは内部的に命令を並べ替えます。

次のステップはスーパースカラ設計でした。プロセッサに同じタイプの実行ユニットを複数搭載することで、 クロックサイクルごとに複数の命令を発行するただし、それらの間に競合がない場合に限ります。内部ディスパッチャは命令の流れを分析し、並列実行可能なものを検出し、それらを複数のユニットに分配します。

これらすべて トリック これらはいわゆる 指導的並列性(ILP)これらの技術の実際的な限界と、消費電力と発熱を大幅に増加させずにクロック速度をさらに上げることが困難になったため、ある時点でメーカーは... にも投資し始めました。 タスクレベルの並列処理: チップあたり複数のスレッドと複数のコア(および コアの駐車場).

これが彼らの誕生の仕方だ マルチコアプロセッサ ハードウェア マルチスレッドを備えたアーキテクチャでは、各コアが複数の実行スレッドの状態を維持し、一部のスレッドがメモリからのデータを待機している間にそれらのスレッドをすばやく切り替えて内部リソースをより有効に活用できます。

クロック周波数の役割とその物理的限界

クロックに戻ると、プロセッサを同期させる信号は、最終的には チップを介して伝播する電気信号周波数が高くなり、トランジスタの数が増えるにつれて、信号全体を完全に整合させることは非常に困難になります。クロック分配、位相シフト、信号整合性の問題が発生します。

一方、クロック遷移ごとに、プロセッサの特定の領域がその時点では何も実行していない場合でも、多数のトランジスタの状態が変化します。これは、 エネルギー消費と熱放散 メトロノームを動かし続けるためだけに、クロックゲーティングなどの技術が導入されました。クロックゲーティングは、未使用のブロックのクロック信号を選択的にオフにすることで、消費電力を削減します。

しかし、ある一定のしきい値を超えると、周波数を上げることは合理的ではなくなり、消費、温度、クロック分配に関する問題が急増します。 そのボトルネック これが、グローバル クロックを完全にまたは部分的に廃止するというアイデアが検討されている理由の 1 つです。ここで、非同期または「クロックレス」設計が登場します。

非同期設計では、単一のクロックで 時間 チップ全体について、 操作を同期させるのはデータと制御信号そのものであるブロックは、要求および確認プロトコル (ハンドシェイク) を使用して通信します。データの準備ができると、プロデューサーがコンシューマーに通知し、コンシューマーは固定クロック エッジを待たずに反応します。

それらは建設された 完全非同期プロセッサ ARMベースのAMULETファミリーやMIPS派生プロジェクトなどの既知の命令セットと互換性があります。また、特定のユニット(例えば特定のALU)のみがグローバルクロックなしで動作し、プロセッサの残りの部分は同期を維持するハイブリッド設計もあります。

クロックレスセキュリティとはどういう意味ですか?

クロックレスセキュリティについて話すとき、2つの考え方が混在しています。一方では、非同期設計として 消費と熱を削減する技術一方、システムの動作を分析、監視し、攻撃や障害から保護する際には、クロックを省略することになります。

同期システムでは、多くのセキュリティおよび監視ツールは、 安定した予測可能な時間リズムサイクルを数えたり、特定の操作にかかる時間を測定したり、一定であるはずの時間の変化を測定することで異常な動作を検出したりするのは比較的簡単です。

非同期システムや部分的にクロックレスなシステムでは、こうした厳密な時間参照は薄れてしまいます。操作の実行時間は、データの実際の可用性、特定の内部経路の混雑、あるいはわずかな物理的変動に左右される可能性があります。攻撃者の観点から見ると、これは非常に大きな問題となります。 タイミングベースのサイドチャネル攻撃の実行がより困難になる共通の基準となるグローバル クロックが消えてしまうためです。

しかし、この動的な性質は、システム内部を監視・監査しようとする人にとっても問題を複雑化させます。多くのプローブやハードウェアカウンタはクロックサイクルに基づいて動作するように設計されており、明確なグローバルクロックがなければ、 パフォーマンスを測定し、疑わしい活動を検出する その場合、他のメトリックとメカニズムが必要になります。

さらに、非同期設計はクロックから解放されるため、データパスが実行ごとにわずかに異なるタイミングでアクティブ化される可能性があり、 一時的な漏れをランダム化する しかし、それはまた、たとえば電力分析攻撃に悪用される可能性のある、異なるより複雑なエネルギー消費パターンの形で、他の扉を開く可能性もあります。

データ表現、ワードサイズ、セキュリティ

CPUアーキテクチャに関連するもう一つの重要な要素は、データの表現方法と処理方法です。ほぼすべての現代のプロセッサは バイナリ表現電圧値は0と1に対応します。ワードサイズ(8、16、32、64ビット…)によって、直接処理できる整数の範囲とアドレス指定可能なメモリの量が決まります。

セキュリティの観点から、ワードサイズはアドレス空間と、 衝突、オーバーフロー、ポインタエラー2^32通りのアドレスを持つ32ビットシステムは、64ビットシステムと比べて非常に明確な制限があります。さらに、特定の保護メモリ拡張など、多くの最新の保護メカニズムは、広大なアドレス空間を必要とします。

MMUとアドレス変換の使用は、プログラムと物理メモリの間に追加の層を導入します。これは、 プロセスを分離する仮想メモリを実装し、カーネルを保護します。非同期コンテキストでは、セキュリティホールや競合状態の発生を回避するために、これらの変換とクロックレスブロック間のハンドシグナルの調整を非常に適切に設計する必要があります。

一方、ベクトル拡張(SIMD)と浮動小数点ユニットは、大量のデータを並列に処理することを可能にします。これは諸刃の剣です。 暗号化アルゴリズムと分析タスクを高速化します。一方、悪意を持って悪用された場合、弱い暗号を解読したり、ブルートフォース攻撃を開始したりするための大きな計算能力が提供されます。

クロックレスまたは部分的に非同期のシナリオでは、これらの並列計算ユニットをプログラムし保護する方法は、次の点を考慮する必要があります。 実行と消費のパターンは、もはや時計によって決まる固定のリズムには従いません。しかし、データの実際のダイナミクスに応答し、サイドチャネルに対する対策の設計にも影響を与えます。

大規模並列処理、マルチスレッド、ベクトル:クロックレスセキュリティへの影響

現代のプロセッサは、クロック速度を上げるだけでなく、より多くの作業を並列処理することでパフォーマンスを向上させることを目指しています。これには、複数のコア、ハードウェアマルチスレッド、そして 命令ごとに複数のデータポイントを処理できるベクトルユニットこれに加えて、GPU、DSP、TPU などの特定のアクセラレータの台頭もあります。

セキュリティの観点から見ると、新たな実行ブロックと新たな並列処理レベルは、保護すべき領域を増やすことになります。そのため、調整が不可欠です。 キャッシュの一貫性、共有メモリ管理、相互排除メカニズムを採用し、スレッド間または同時プロセス間の競合状態や情報漏洩を回避します。

クロックレス環境やハイブリッド環境では、この調整はグローバルクロックサイクルよりもブロック間の通信プロトコルに依存します。例えば、カーネルは 要求と認識の信号 メモリまたは共有リソースにアクセスするには、実際の遅延は固定されたサイクル数ではなく、その時点の実際のトラフィックに依存します。

この動作は、外部から見ると、クロックサイクル数に基づく非常に正確な時間測定に依存する特定の攻撃を困難にします。しかし同時に、セキュリティ設計者はサイクルカウントにとどまらず、… イベントカウンター、トラフィック測定、エネルギー消費 不審な行動を検出するためのその他の兆候。

そのため、多くのメーカーは、キャッシュミス、分岐予測の失敗、特定のメモリアクセスなどをリアルタイムで監視できるハードウェア パフォーマンス カウンターを統合しています。これらのカウンターは、正しく使用すれば、パフォーマンスの最適化と... の両方を実現する強力なツールになります。 異常なパターンを見つける の特徴 マルウェア または、部分的に非同期のアーキテクチャであっても、高度なエクスプロイトを実行できます。

現代の環境における仮想化、vCPU、分離

今日の環境におけるもう一つの重要な要素は仮想化です。クラウドでは、私たちは常に 仮想CPU(vCPU)、割り当てられた処理能力の論理的な断片である 仮想マシン または、共有物理ハードウェア上のコンテナ。

各vCPUは、基本的にハイパーバイザーが物理コア上でスケジュールするスレッドまたは実行時間の集合です。これがうまく機能するために、物理CPUは次のような機能を提供します。 特別な特権モード ハイパーバイザーが作成および分離できるようにする 仮想マシン特定の機密指示を傍受し、ゲスト同士が干渉したりスパイしたりできないように各ゲストのメモリを管理します。

この文脈では、クロックレスセキュリティとは、仮想マシン間のCPU時間の割り当てが均一なクロックだけでなく、 より動的な計画メカニズム ハードウェアでサポートされているクロックサイクル。ハイパーバイザーはクロックサイクルを認識しますが、それらのサイクルが各コアで有効な処理にどのように変換されるかは、内部の非同期ブロックによって変更できます。

セキュリティの観点からは、単にティックをカウントするだけでなく、パフォーマンス カウンター、使用状況統計、低レベルのイベントも解釈できる監視ツールの設計が必要になります。 リソースの不正使用、仮想マシンのエスケープ、不規則なパターンを検出する 侵入を示唆するものです。

さらに、ベクトルユニット、GPU、その他のアクセラレータがフル活用される計算集約型の環境では、セキュリティ管理者は、同期型か非同期型かを問わず、これらのブロックが次のようなツールになる可能性があることを考慮する必要があります。 暗号攻撃を加速し、 ユーザーの知らないうちに暗号通貨を採掘する または、盗まれた大量のデータの分析を実行します。

パフォーマンス、消費電力、オーバークロックとクロックなしの設計との比較

最後に、パフォーマンスと消費電力の関係を考慮する必要があります。オーバークロック(例えば、 OCCTによる安定性テスト)はCPU 1秒あたりに実行する操作数を増やすしかし、これは消費電力と温度を大幅に増加させます。実際、多くの現行プロセッサは、ワークロードと内部温度に基づいて周波数と電圧を動的に調整しています。

非同期設計は代替案を提供します。非常に高速なクロックを使用してすべてを位相合わせしようとする代わりに、 各ブロックがデータによって決定されたペースで機能できるようにします。負荷が低い期間中、非アクティブな部分の状態はほとんど変化しないため、複雑なクロックベースの電源管理メカニズムを必要とせずに消費が削減されます。

安全性の観点から見ると、消費量と発熱量の削減は、単に環境問題や電気代の問題だけではありません。それはまた、 部品への負担が少ないエレクトロマイグレーションや電流漏れによって引き起こされる障害の可能性が低くなり、極端な温度や電圧条件下でのシステムの動作を悪用しようとする攻撃を受ける可能性が低くなります。

しかし、完全に非同期で安全なシステムの設計は容易ではありません。ブロック間の通信プロトコル、競合状態、中間状態を厳密に検証し、エラーを防ぐ必要があります。 攻撃者が悪用できる非決定論的な動作設計の複雑さ、成熟したツールの不足、既存のソフトウェアとの下位互換性の必要性により、当面、ほとんどの商用プロセッサは、小さな非同期アイランドを備えた同期型のままとなっています。

内部アーキテクチャ、クロック管理、並列処理、仮想化、そして電力といったあらゆる要素が組み合わさることで、グローバルクロックを持たない環境におけるセキュリティは繊細なバランスを要求されます。非同期設計は、特定のタイミングベースの攻撃を軽減し、高度に洗練された省電力戦略を可能にしますが、同時にハードウェアの動作の監視、監査、検証において新たな課題も生み出します。そのため、鍵となるのは統合です。 堅牢な観測性と分離メカニズム シリコン自体から最高レベルのソフトウェアまで。

バイトの世界とテクノロジー全般についての情熱的なライター。私は執筆を通じて自分の知識を共有するのが大好きです。このブログでは、ガジェット、ソフトウェア、ハードウェア、技術トレンドなどについて最も興味深いことをすべて紹介します。私の目標は、シンプルで楽しい方法でデジタル世界をナビゲートできるよう支援することです。