- ระบบรักษาความปลอดภัยแบบไร้สัญญาณนาฬิกาเกี่ยวข้องกับการออกแบบซีพียูแบบอะซิงโครนัส ซึ่งการพึ่งพาสัญญาณนาฬิกาสากลจะลดลงหรือหมดไป

- โปรเซสเซอร์สมัยใหม่ผสานรวมแคช หน่วยจัดการหน่วยความจำ (MMU) การประมวลผลแบบขนาน และเธรดหลายตัว ซึ่งทำให้ทั้งประสิทธิภาพและความปลอดภัยซับซ้อนยิ่งขึ้น

- การออกแบบที่ไม่ใช้กลไกนาฬิกาสามารถลดโอกาสการโจมตีแบบจับเวลาได้ แต่จำเป็นต้องมีรูปแบบการตรวจสอบและการตรวจสอบแบบใหม่ ฮาร์ดแวร์.

- เทคโนโลยีเวอร์ชวลไลเซชัน, vCPU และตัวเร่งความเร็วเฉพาะทาง ขยายขอบเขตช่องโหว่ด้านความปลอดภัย ทำให้การบูรณาการระบบรักษาความปลอดภัยตั้งแต่ระดับซิลิคอนเป็นสิ่งจำเป็นอย่างยิ่ง

การแสดงออก ระบบรักษาความปลอดภัยแบบไร้นาฬิกาฟังดูเหมือนแนวคิดแห่งอนาคตแต่จริงๆ แล้วมันมีความเกี่ยวข้องอย่างใกล้ชิดกับวิธีการออกแบบและปกป้องโปรเซสเซอร์และระบบในปัจจุบัน เพื่อให้เข้าใจอย่างถูกต้อง เราจำเป็นต้องเจาะลึกเข้าไปในวิธีการทำงานภายในของ CPU วิธีการจัดระเบียบการประมวลผลคำสั่ง และบทบาทของสัญญาณนาฬิกาที่มีชื่อเสียงในการกำหนดจังหวะการทำงานของระบบทั้งหมด

ในช่วงหลายทศวรรษที่ผ่านมา หน่วยประมวลผลต่างแข่งขันกันเพื่อเพิ่มความเร็วให้มากขึ้น ความถี่สัญญาณนาฬิกา รวมทรานซิสเตอร์ให้มากขึ้น และเพิ่มจำนวนการทำงานแบบขนานในขณะเดียวกัน ก็มีการออกแบบที่พยายามหลุดพ้นจากการพึ่งพาเวลาสากล ไม่ว่าจะเป็นทั้งชิปหรือในบางส่วนโดยเฉพาะ พื้นที่นี้ ซึ่งก็คือการออกแบบแบบอะซิงโครนัสหรือแบบไร้เวลา (clockless) เปิดโอกาสที่น่าสนใจอย่างมากในแง่ของการใช้พลังงานและการระบายความร้อน… และยังรวมถึงความท้าทายด้านความปลอดภัยเฉพาะด้าน ซึ่งมักถูกจัดกลุ่มอยู่ภายใต้แนวคิดของความปลอดภัยแบบไร้เวลา (clockless security)

ซีพียูเป็นศูนย์กลางของระบบและมีความสัมพันธ์กับนาฬิกา

เมื่อพูดถึงเรื่องความปลอดภัยที่เกี่ยวข้องกับนาฬิกา สิ่งแรกที่ต้องจำไว้คือ CPU คืออะไรกันแน่ โดยพื้นฐานแล้ว CPU ก็คือ... หน่วยประมวลผลกลางคือสมองของคอมพิวเตอร์: ส่วนประกอบที่ตีความและประมวลผลคำสั่งโปรแกรม ประสานงานหน่วยความจำ การรับ/ส่งข้อมูล และหน่วยประมวลผลร่วมเฉพาะทาง เช่น GPU

ภายในซีพียูสมัยใหม่ เราจะพบส่วนประกอบที่แตกต่างกันหลายส่วน ในด้านหนึ่ง มี... หน่วยคำนวณและตรรกะ (ALU)หน่วยคำนวณและตรรกะ (ALU) มีหน้าที่รับผิดชอบในการดำเนินการทางคณิตศาสตร์และตรรกะกับจำนวนเต็ม นอกจากนี้ยังมีรีจิสเตอร์ ซึ่งเป็นหน่วยความจำขนาดเล็กและเร็วมากที่ใช้เก็บข้อมูลที่โปรเซสเซอร์กำลังประมวลผลอยู่ และเหนือสิ่งอื่นใด คือหน่วยควบคุมที่ทำหน้าที่ตัดสินใจในแต่ละรอบการทำงาน ว่าจะทำอะไร อ่านอะไรจากหน่วยความจำ และเขียนอะไรลงไป

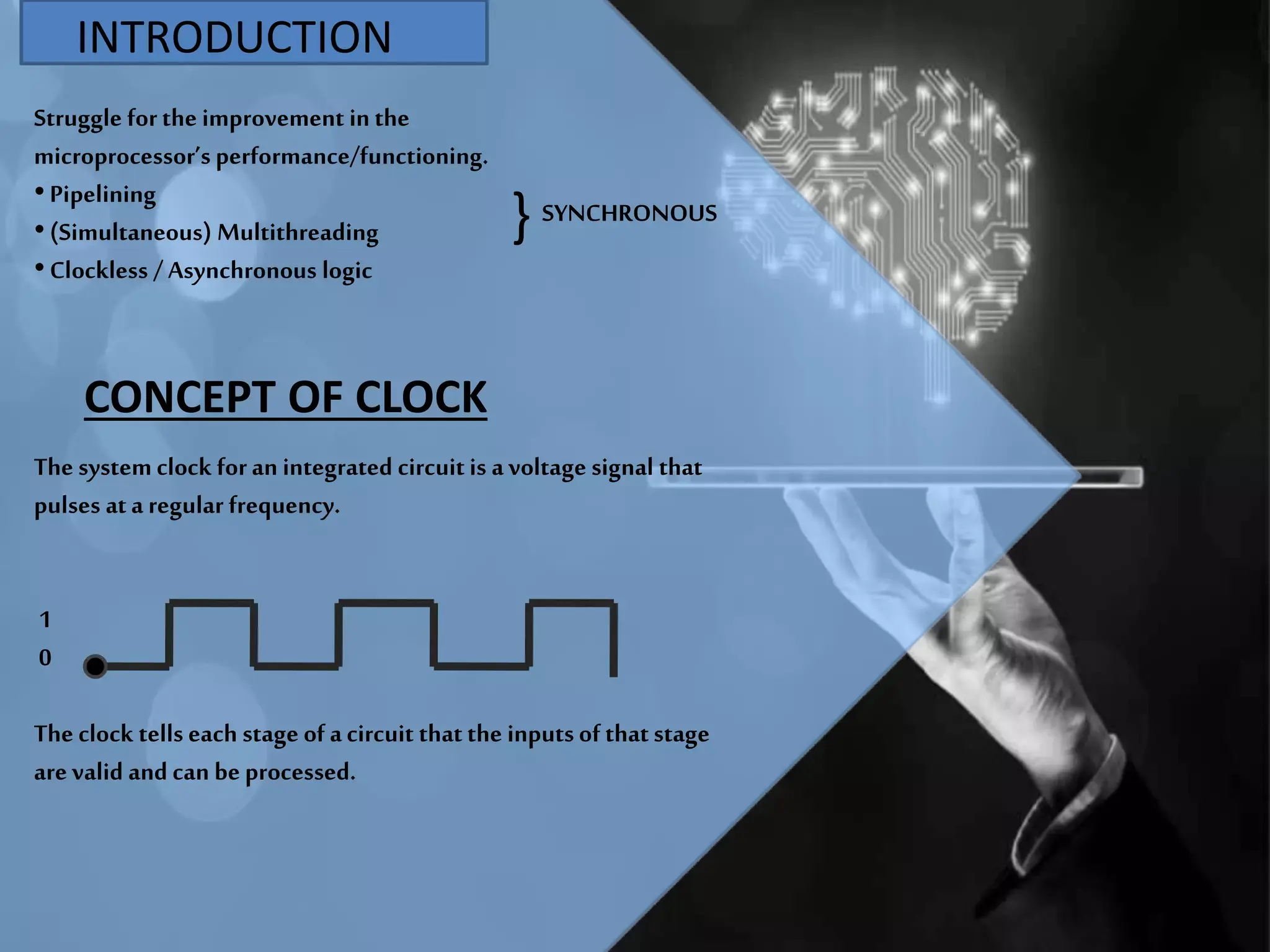

โปรเซสเซอร์สมัยใหม่ส่วนใหญ่มีดีไซน์แบบซิงโครนัส ซึ่งหมายความว่าบล็อกภายในทั้งหมดจะถูกประสานงานโดยใช้ สัญญาณนาฬิกาแบบคาบเป็นเหมือนเครื่องกำหนดจังหวะการทำงานแบบอิเล็กทรอนิกส์ แต่ละจังหวะของนาฬิกานี้จะก้าวไปหนึ่งขั้นในสิ่งที่เรียกว่าวงจรคำสั่ง: คำสั่งจะถูกดึงมา ถอดรหัส ประมวลผล ผลลัพธ์จะถูกจัดเก็บ และวงจรก็จะเริ่มต้นใหม่อีกครั้ง

ในโปรเซสเซอร์แบบดั้งเดิม สัญญาณนาฬิกาถูกสร้างขึ้นโดยออสซิลเลเตอร์ภายนอกที่ส่งพัลส์หลายล้านหรือหลายพันล้านพัลส์ต่อวินาที ความถี่ของพัลส์เหล่านี้ ซึ่งวัดเป็นเฮิร์ตซ์ เมกะเฮิร์ตซ์ หรือกิกะเฮิร์ตซ์ จะบอกเราว่าซีพียูมี "รอบการทำงาน" กี่รอบต่อวินาทีเพื่อเคลื่อนย้ายข้อมูลและดำเนินการต่างๆ ยิ่งความถี่สัญญาณนาฬิกาสูงเท่าไร ก็ยิ่งสามารถทำงานต่อวินาทีได้มากขึ้นเท่านั้นโดยมีเงื่อนไขว่าสถาปัตยกรรมส่วนอื่นๆ ต้องสอดคล้องกันด้วย

ดังนั้น ประสิทธิภาพจึงไม่ได้ขึ้นอยู่กับความเร็วของนาฬิกาเพียงอย่างเดียว แต่ยังขึ้นอยู่กับจำนวนนาฬิกาด้วย คำสั่งต่อรอบ (IPC) มันสามารถทำงานให้เสร็จสมบูรณ์ได้ ผลคูณของความถี่กับจำนวนคำสั่งต่อรอบ (IPC) ช่วยให้เราทราบถึงจำนวนคำสั่งหลายล้านคำสั่งต่อวินาทีที่มันสามารถประมวลผลได้ แม้ว่าตัวเลขทางทฤษฎีมักจะมองโลกในแง่ดีมากกว่าสิ่งที่เห็นได้จริงจากโปรแกรมจริงก็ตาม

จากระบบสายไฟแบบตายตัว สู่ไมโครโปรเซสเซอร์แบบรวมวงจร

เพื่อให้เข้าใจถึงการออกแบบที่ไม่มีนาฬิกาได้ดีขึ้น จำเป็นต้องทบทวนวิวัฒนาการของซีพียู คอมพิวเตอร์อิเล็กทรอนิกส์ยุคแรก เช่น ENIAC นั้น เครื่องจักรแบบโปรแกรมคงที่ที่เชื่อมต่อด้วยสายไฟในการเปลี่ยนภารกิจ ระบบจะต้องได้รับการเชื่อมต่อสายไฟใหม่ทางกายภาพ แนวคิดที่ปฏิวัติวงการคือคอมพิวเตอร์แบบโปรแกรมจัดเก็บ ซึ่งคำสั่งต่างๆ จะถูกเก็บไว้ในหน่วยความจำ โปรเซสเซอร์เพียงแค่จะอ่านและประมวลผลคำสั่งเหล่านั้น

สถาปัตยกรรมโปรแกรมที่จัดเก็บไว้ซึ่งเกี่ยวข้องกับจอห์น ฟอน นอยมันน์ ในที่สุดก็ได้รับชัยชนะ ในสถาปัตยกรรมนั้น คำสั่งและข้อมูลใช้พื้นที่หน่วยความจำร่วมกันแตกต่างจากสถาปัตยกรรมฮาร์วาร์ดซึ่งแยกข้อมูลทั้งสองประเภทออกจากกันทางกายภาพ ปัจจุบันซีพียูอเนกประสงค์เกือบทั้งหมดใช้สถาปัตยกรรมฟอน นอยมันน์ แม้ว่าจะมีโปรเซสเซอร์ฮาร์วาร์ดแบบบริสุทธิ์หรือแบบไฮบริดจำนวนมากที่ยังคงมีอยู่ในโลกของระบบฝังตัว

หน่วยประมวลผลรุ่นแรกๆ สร้างขึ้นโดยใช้รีเลย์หรือหลอดสุญญากาศ มันมีขนาดใหญ่ เทอะทะ และทำงานช้า ความเชื่อถือได้ มีข้อจำกัดมาก การก้าวกระโดดไปสู่ทรานซิสเตอร์แบบโซลิดสเตทในช่วงทศวรรษ 50 และ 60 ทำให้สิ่งนี้เป็นไปได้ เพิ่มความเร็วอย่างมาก ลดการใช้พลังงาน และลดขนาดลงจากนั้น การเปลี่ยนแปลงก็เกิดขึ้นจากวงจรแบบแยกส่วนไปสู่วงจรแบบรวม (IC) โดยการนำทรานซิสเตอร์จำนวนมากขึ้นเรื่อยๆ มาไว้บนชิปเดียว

ด้วยการถือกำเนิดของวงจรรวม (Integrated Circuit) เริ่มจากขนาดเล็ก (SSI) ตามด้วยขนาดกลาง (MSI) ขนาดใหญ่ (LSI) และสุดท้ายคือขนาดใหญ่มาก (VLSI) ทำให้ CPU มีขนาดเล็ลงจนสามารถบรรจุลงในอุปกรณ์ได้ ทั้งหมดบนชิปตัวเดียวหรือสองสามตัวการบูรณาการนี้ได้นำไปสู่การพัฒนาไมโครโปรเซสเซอร์ ซึ่งหน่วยประมวลผลทั้งหมดถูกผลิตขึ้นบนชิปซิลิคอนชิ้นเดียว

El อินเทล 4004Intel 8080 ซึ่งวางจำหน่ายในปี 1971 เป็นหนึ่งในไมโครโปรเซสเซอร์เชิงพาณิชย์รุ่นแรกๆ ต่อมาได้มีการออกแบบไมโครโปรเซสเซอร์ที่มีประสิทธิภาพสูงกว่าตามมา เช่น Intel 8080 ซึ่งกลายเป็นรากฐานของคอมพิวเตอร์ส่วนบุคคล นับจากนั้นเป็นต้นมา คำว่า CPU จึงถูกใช้เพื่ออ้างถึงไมโครโปรเซสเซอร์เหล่านี้เกือบทุกครั้ง

ส่วนประกอบภายในที่สำคัญของซีพียูสมัยใหม่

ซีพียูสมัยใหม่ได้จัดสรรพื้นที่ผิวซิลิคอนส่วนใหญ่ให้กับองค์ประกอบเสริมต่างๆ ที่ออกแบบมาเพื่อ... เพื่อให้ได้ประโยชน์สูงสุดจากทุกรอบการทำงานของนาฬิกาตัวอย่างเช่น โปรเซสเซอร์เกือบทุกตัวมีแคชหลายระดับ: หน่วยความจำขนาดเล็กแต่เร็วมากซึ่งตั้งอยู่ใกล้กับแกนประมวลผล ทำหน้าที่จัดเก็บสำเนาของข้อมูลที่ใช้บ่อยที่สุด เพื่อที่แกนประมวลผลจะไม่ต้องเข้าถึง RAM อยู่ตลอดเวลา

นอกจากแคช L1, L2 และ L3 แล้ว CPU ที่ซับซ้อนยังประกอบด้วย... หน่วยจัดการหน่วยความจำ (MMU) ซึ่งแปลงที่อยู่เสมือน (ที่ระบบปฏิบัติการจัดการ) ไปเป็นที่อยู่จริงใน RAM และจัดการ... หน่วยความจำเสมือน และช่วยแยกกระบวนการต่างๆ ออกจากกัน

ในระนาบการคำนวณ เรามีหน่วยประมวลผลเฉพาะทางหลายหน่วย ได้แก่ ALU สำหรับจำนวนเต็ม และ... หน่วยประมวลผลจุดลอยตัว (FPU) สำหรับการดำเนินการกับเลขฐานสิบ หน่วยสร้างที่อยู่ (AGU) จะถูกใช้เพื่อคำนวณตำแหน่งหน่วยความจำอย่างรวดเร็ว และในสถาปัตยกรรมหลายๆ แบบ จะใช้หน่วยเวกเตอร์หรือ SIMD เพื่อดำเนินการกับจุดข้อมูลหลายจุดพร้อมกัน

นอกจากนี้ยังมีหน่วยควบคุม ซึ่งอาจเป็นลอจิกแบบต่อสายหรือแบบใช้ไมโครโค้ด กล่าวคือ โปรแกรมภายในที่แปลคำสั่งระดับสูงแต่ละข้อ ในลำดับของสัญญาณควบคุมภายใน ในโปรเซสเซอร์หลายตัว ไมโครโค้ดนี้สามารถอัปเดตได้ ทำให้สามารถแก้ไขข้อผิดพลาดในการออกแบบหรือปรับพฤติกรรมได้ในภายหลัง

สุดท้ายนี้ ยังมีรีจิสเตอร์ภายในจำนวนมาก ได้แก่ รีจิสเตอร์อเนกประสงค์ ตัวสะสม ตัวนับโปรแกรม รีจิสเตอร์สถานะพร้อมแฟล็กที่บ่งชี้สิ่งต่างๆ เช่น ผลลัพธ์ของการดำเนินการเป็นศูนย์ เป็นลบ หรือเกิดการโอเวอร์โฟลว์ เป็นต้น ทั้งหมดนี้ทำงานประสานกันตามลูปแบบคลาสสิก การรับ การถอดรหัส และการดำเนินการตามคำสั่ง.

วิธีการเรียกใช้โปรแกรมทีละขั้นตอน

หลักการทำงานพื้นฐานของ CPU ใดๆ ก็ตาม สรุปได้คือการดึงคำสั่งจากหน่วยความจำและประมวลผลทีละคำสั่ง ซึ่งเกิดขึ้นในสามขั้นตอนหลัก ขั้นแรกคือขั้นตอนของ... จับภาพ (ดึงข้อมูล)ซึ่งเป็นการอ่านคำสั่งที่มีการระบุแอดเดรสโดยตัวนับโปรแกรมจากหน่วยความจำ

ขั้นตอนต่อไปคือการถอดรหัส คำสั่งที่ได้รับมาใหม่จะผ่านตัวถอดรหัสไบนารีซึ่งจะตรวจสอบรหัสการทำงาน (opcode) และ แปลงรูปแบบบิตนั้นให้เป็นสัญญาณที่เป็นรูปธรรม นั่นคือส่วนที่จะเปิดใช้งานหรือปิดใช้งานส่วนต่างๆ ของโปรเซสเซอร์ ซึ่งเป็นส่วนที่จะตัดสินว่าเป็นการบวก การกระโดด การโหลดจากหน่วยความจำ ฯลฯ และเกี่ยวข้องกับรีจิสเตอร์หรือแอดเดรสใดบ้าง

สุดท้าย การดำเนินการจะถูกดำเนินการ หน่วยคำนวณและตรรกะ (ALU) หรือหน่วยที่เกี่ยวข้องจะทำการคำนวณหรือเคลื่อนย้ายข้อมูล และผลลัพธ์มักจะถูกเก็บไว้ในรีจิสเตอร์หรือในหน่วยความจำ หากจำเป็นต้องเปลี่ยนแปลงการไหลของโปรแกรม เช่น การกระโดดแบบมีเงื่อนไข ตัวนับโปรแกรมจะได้รับการอัปเดตด้วยที่อยู่ใหม่ ชุดของ คำสั่ง ข้อมูล และการกระโดด มันเป็นส่วนที่ก่อให้เกิดลูป ฟังก์ชัน เงื่อนไข และตรรกะทั้งหมดของโปรแกรมของเรา

ในโปรเซสเซอร์แบบง่าย ทุกอย่างเกิดขึ้นอย่างเป็นเส้นตรงและเรียงลำดับ แต่ในซีพียูสมัยใหม่ ขั้นตอนเหล่านี้หลายขั้นตอนมีการซ้อนทับกันโดยใช้เทคนิคการทำงานแบบขนานเป้าหมายคือให้แต่ละรอบการทำงานของนาฬิกาทำงานให้ได้มากที่สุดเท่าที่จะเป็นไปได้ และฮาร์ดแวร์ต้องไม่หยุดทำงาน

ความขนาน การส่งผ่าน และการดำเนินการที่ไม่เป็นลำดับ

เพื่อไม่ให้สิ้นเปลืองนาฬิกา นักออกแบบจึงได้แนะนำ... การประมวลผลคำสั่งแบบไปป์ไลน์เส้นทางการประมวลผลข้อมูลถูกแบ่งออกเป็นหลายขั้นตอน คล้ายกับสายการผลิต ในขณะที่คำสั่งหนึ่งกำลังถูกถอดรหัส คำสั่งถัดไปก็กำลังถูกดึงมาจากหน่วยความจำ และอาจมีอีกคำสั่งหนึ่งกำลังประมวลผลอยู่ในหน่วยคำนวณและตรรกะ (ALU)

ปัญหาคือบางครั้งคำสั่งหนึ่งต้องการผลลัพธ์จากอีกคำสั่งหนึ่งที่ยังประมวลผลไม่เสร็จ ซึ่งก่อให้เกิดการพึ่งพาข้อมูลและบังคับให้เกิดการหยุดชะงักหรือการรอคอยในไปป์ไลน์ เพื่อลดความล่าช้าเหล่านี้ จึงมีการใช้เทคนิคต่างๆ เช่น การส่งต่อตัวดำเนินการ การคาดการณ์การแตกแขนง และในภายหลังคือ... การดำเนินการนอกลำดับซึ่งโปรเซสเซอร์จะจัดเรียงลำดับคำสั่งใหม่ภายในตราบใดที่ผลลัพธ์สุดท้ายของโปรแกรมยังคงเหมือนเดิม

ขั้นตอนต่อไปคือการออกแบบซูเปอร์สเกลาร์: การติดตั้งหน่วยประมวลผลหลายหน่วยที่มีประเภทเดียวกันไว้ในโปรเซสเซอร์ เพื่อให้สามารถ ออกคำสั่งหลายคำสั่งต่อรอบสัญญาณนาฬิกาโดยมีเงื่อนไขว่าต้องไม่มีข้อขัดแย้งระหว่างกัน ตัวจัดการภายในจะวิเคราะห์ลำดับคำสั่ง ตรวจจับสิ่งที่สามารถดำเนินการพร้อมกันได้ และกระจายคำสั่งเหล่านั้นไปยังหน่วยต่างๆ

ทั้งหมดนี้ เล่นกล สิ่งเหล่านี้รวมอยู่ในสิ่งที่เรียกว่า ความขนานเชิงการสอน (ILP)ข้อจำกัดในทางปฏิบัติของเทคนิคเหล่านี้และความยากลำบากที่เพิ่มขึ้นในการเพิ่มความเร็วสัญญาณนาฬิกาโดยไม่เพิ่มการใช้พลังงานและความร้อนอย่างมีนัยสำคัญ ทำให้ ณ จุดหนึ่ง ผู้ผลิตเริ่มลงทุนใน... ความขนานระดับงาน: เธรดหลายตัวและคอร์หลายตัวต่อชิป (และกลไกต่างๆ เช่น ที่จอดรถสำหรับแกนกลาง).

นี่คือวิธีที่พวกเขาเกิดมา โปรเซสเซอร์แบบมัลติคอร์ และสถาปัตยกรรมที่มีการประมวลผลแบบมัลติเธรดด้วยฮาร์ดแวร์ ซึ่งแต่ละคอร์สามารถรักษาสถานะของเธรดการทำงานหลายเธรดและสลับไปมาระหว่างเธรดเหล่านั้นได้อย่างรวดเร็วเพื่อใช้ทรัพยากรภายในให้เกิดประโยชน์สูงสุด ในขณะที่เธรดบางส่วนรอข้อมูลจากหน่วยความจำ

บทบาทของความถี่สัญญาณนาฬิกาและข้อจำกัดทางกายภาพ

กลับมาที่เรื่องนาฬิกา สิ่งสำคัญที่ควรทราบคือ สัญญาณที่ใช้ในการซิงโครไนซ์โปรเซสเซอร์นั้น ในที่สุดแล้วก็คือ... สัญญาณไฟฟ้าที่แพร่กระจายผ่านชิปเมื่อความถี่เพิ่มขึ้นและจำนวนทรานซิสเตอร์มากขึ้น การรักษาให้สัญญาณอยู่ในแนวเดียวกันอย่างสมบูรณ์แบบตลอดทั้งระบบจึงกลายเป็นเรื่องยากมาก ปัญหาเกี่ยวกับการกระจายสัญญาณนาฬิกา การเลื่อนเฟส และความสมบูรณ์ของสัญญาณจึงเกิดขึ้น

ในทางกลับกัน การเปลี่ยนสถานะของสัญญาณนาฬิกาแต่ละครั้งทำให้ทรานซิสเตอร์จำนวนมากเปลี่ยนสถานะ แม้ว่าส่วนใดส่วนหนึ่งของโปรเซสเซอร์จะไม่ได้ทำงานที่เป็นประโยชน์ในขณะนั้นก็ตาม ซึ่งหมายความว่า การใช้พลังงานและการระบายความร้อน เพียงเพื่อให้จังหวะเมโทรโนมทำงานอย่างต่อเนื่อง เพื่อแก้ไขปัญหานี้ จึงมีการนำเทคนิคต่างๆ เช่น การควบคุมสัญญาณนาฬิกา (clock gating) มาใช้ ซึ่งจะปิดสัญญาณนาฬิกาในส่วนที่ไม่ได้ใช้งานอย่างเลือกสรร ช่วยลดการใช้พลังงาน

อย่างไรก็ตาม เมื่อความถี่สูงเกินระดับหนึ่ง การเพิ่มความถี่จะไม่ใช่เรื่องที่สมเหตุสมผลอีกต่อไป เนื่องจากปัญหาด้านการใช้พลังงาน อุณหภูมิ และการกระจายเวลาจะเพิ่มสูงขึ้นอย่างมาก ปัญหาคอขวดนั้น นี่เป็นหนึ่งในเหตุผลที่ทำให้มีการสำรวจแนวคิดเรื่องการยกเลิกการใช้สัญญาณนาฬิกาสากลทั้งหมดหรือบางส่วน ซึ่งเป็นจุดที่การออกแบบแบบอะซิงโครนัสหรือ "ไร้สัญญาณนาฬิกา" เข้ามามีบทบาท

ในการออกแบบแบบอะซิงโครนัส แทนที่จะใช้สัญญาณนาฬิกาเพียงตัวเดียวในการกำหนดตำแหน่ง เวลา สำหรับชิปทั้งหมด ข้อมูลและสัญญาณควบคุมเหล่านั้นเองที่เป็นตัวประสานการทำงานต่างๆบล็อกต่างๆ สื่อสารกันโดยใช้โปรโตคอลการร้องขอและการยืนยัน (การจับมือ): เมื่อข้อมูลพร้อม ผู้ผลิตจะแจ้งให้ผู้บริโภคทราบ และผู้บริโภคจะตอบสนองโดยไม่ต้องรอจังหวะสัญญาณนาฬิกาที่แน่นอน

สิ่งเหล่านั้นถูกสร้างขึ้น โปรเซสเซอร์แบบอะซิงโครนัสโดยสมบูรณ์ สามารถใช้งานร่วมกับชุดคำสั่งที่รู้จักกันดี เช่น ตระกูล AMULET ที่ใช้สถาปัตยกรรม ARM หรือโครงการที่พัฒนามาจาก MIPS นอกจากนี้ยังมีดีไซน์แบบไฮบริด ซึ่งมีเพียงบางหน่วย (เช่น หน่วยคำนวณและตรรกะเฉพาะ) เท่านั้นที่ทำงานโดยไม่ต้องใช้สัญญาณนาฬิกาส่วนกลาง ในขณะที่ส่วนที่เหลือของโปรเซสเซอร์ยังคงทำงานแบบซิงโครนัส

ระบบรักษาความปลอดภัยแบบไร้นาฬิกาหมายความว่าอย่างไร?

เมื่อพูดถึงระบบรักษาความปลอดภัยที่ไม่ขึ้นกับนาฬิกา มักมีการผสมผสานแนวคิดสองอย่างเข้าด้วยกัน คือ ในด้านหนึ่ง การออกแบบแบบอะซิงโครนัส เทคนิคในการลดการใช้พลังงานและความร้อนในทางกลับกัน การไม่คำนึงถึงเวลาเมื่อวิเคราะห์ ตรวจสอบ และปกป้องพฤติกรรมของระบบจากการโจมตีหรือความล้มเหลวก็อาจส่งผลเสียได้เช่นกัน

ในระบบซิงโครนัส เครื่องมือรักษาความปลอดภัยและการตรวจสอบจำนวนมากอาศัยการมีอยู่ของ จังหวะเวลาที่คงที่และคาดการณ์ได้การนับรอบ การวัดระยะเวลาในการดำเนินการบางอย่าง หรือการพยายามตรวจจับพฤติกรรมที่ผิดปกติโดยการวัดความแปรผันของเวลาที่ควรจะคงที่นั้นค่อนข้างง่าย

ในระบบแบบอะซิงโครนัสหรือระบบที่ไม่มีนาฬิกาอย่างสมบูรณ์ การอ้างอิงเวลาที่ตายตัวเหล่านี้จะลดทอนลง เวลาในการดำเนินการอาจขึ้นอยู่กับความพร้อมใช้งานของข้อมูลจริง ความแออัดบนเส้นทางภายในบางเส้นทาง หรือการเปลี่ยนแปลงทางกายภาพเล็กน้อย จากมุมมองของผู้โจมตี สิ่งนี้อาจทำให้ การโจมตีแบบ side-channel ที่อาศัยจังหวะเวลาทำได้ยากขึ้นเนื่องจากนาฬิกาสากลซึ่งทำหน้าที่เป็นจุดอ้างอิงร่วมกันได้หายไป

อย่างไรก็ตาม ลักษณะพลวัตนี้ก็ทำให้เรื่องยุ่งยากขึ้นสำหรับผู้ที่ต้องการสังเกตและตรวจสอบระบบจากภายใน อุปกรณ์ตรวจวัดและตัวนับฮาร์ดแวร์จำนวนมากถูกออกแบบมาให้ทำงานตามรอบสัญญาณนาฬิกา หากไม่มีสัญญาณนาฬิกาหลักที่ชัดเจน... วัดประสิทธิภาพและตรวจจับกิจกรรมที่น่าสงสัย จากนั้นจึงต้องใช้ตัวชี้วัดและกลไกอื่นๆ เพิ่มเติม

นอกจากนี้ การออกแบบแบบอะซิงโครนัสซึ่งไม่ขึ้นอยู่กับนาฬิกา ทำให้สามารถเปิดใช้งานเส้นทางข้อมูลได้ในเวลาที่แตกต่างกันเล็กน้อยในแต่ละรอบการทำงาน ซึ่งอาจส่งผลให้... สุ่มการรั่วไหลชั่วคราว แต่ก็อาจเปิดช่องทางอื่นๆ ได้เช่นกัน ตัวอย่างเช่น ในรูปแบบของรูปแบบการใช้พลังงานที่แตกต่างและซับซ้อนมากขึ้น ซึ่งอาจถูกใช้ประโยชน์ในการโจมตีด้วยการวิเคราะห์พลังงานได้

การนำเสนอข้อมูล ขนาดคำ และความปลอดภัย

ปัจจัยสำคัญอีกประการหนึ่งที่เกี่ยวข้องกับสถาปัตยกรรมของ CPU คือวิธีการแสดงและจัดการข้อมูล โปรเซสเซอร์สมัยใหม่เกือบทั้งหมดใช้ การแสดงผลแบบไบนารีโดยมีค่าแรงดันไฟฟ้าที่สอดคล้องกับ 0 และ 1 ขนาดของคำ (8, 16, 32, 64 บิต…) จะกำหนดช่วงของจำนวนเต็มที่สามารถจัดการได้โดยตรงและปริมาณของหน่วยความจำที่สามารถเข้าถึงได้

จากมุมมองด้านความปลอดภัย ขนาดของคำมีผลต่อพื้นที่แอดเดรสและความน่าจะเป็นของการโจมตี การชนกัน การล้น และข้อผิดพลาดของตัวชี้ระบบ 32 บิตที่มีแอดเดรสที่เป็นไปได้ 2^32 ตัว มีข้อจำกัดที่ชัดเจนมากเมื่อเทียบกับระบบ 64 บิต ยิ่งไปกว่านั้น กลไกการป้องกันสมัยใหม่หลายอย่าง เช่น ส่วนขยายหน่วยความจำที่ได้รับการป้องกันบางประเภท อาศัยพื้นที่แอดเดรสขนาดใหญ่

การใช้ MMU และการแปลงที่อยู่ยังเป็นการเพิ่มชั้นพิเศษระหว่างโปรแกรมและหน่วยความจำทางกายภาพ ซึ่งเป็นสิ่งสำคัญอย่างยิ่งสำหรับ กระบวนการแยกใช้หน่วยความจำเสมือนและปกป้องเคอร์เนล ในบริบทแบบอะซิงโครนัส การประสานงานระหว่างการแปลงเหล่านี้และสัญญาณมือระหว่างบล็อกที่ไม่มีนาฬิกาจะต้องได้รับการออกแบบมาอย่างดีเพื่อหลีกเลี่ยงการสร้างช่องโหว่ด้านความปลอดภัยหรือสภาวะการแข่งขัน

ในทางกลับกัน ส่วนขยายเวกเตอร์ (SIMD) และหน่วยประมวลผลทศนิยมช่วยให้สามารถทำงานกับข้อมูลปริมาณมากได้พร้อมกัน นี่เป็นดาบสองคม: ในด้านหนึ่ง ช่วยเร่งความเร็วของอัลกอริธึมการเข้ารหัสและงานวิเคราะห์ในทางกลับกัน หากถูกนำไปใช้ในทางที่ผิด มันจะมอบพลังการประมวลผลมหาศาลเพื่อถอดรหัสลับที่อ่อนแอ หรือใช้โจมตีแบบเดาสุ่ม (brute-force attack)

ในสถานการณ์ที่ไม่มีนาฬิกาหรือมีการทำงานแบบอะซิงโครนัสบางส่วน วิธีการเขียนโปรแกรมและการป้องกันหน่วยประมวลผลแบบขนานเหล่านี้จะต้องคำนึงถึงสิ่งต่อไปนี้ รูปแบบการดำเนินการและการบริโภคไม่ได้เป็นไปตามจังหวะเวลาที่กำหนดโดยนาฬิกาอีกต่อไปแต่จะตอบสนองต่อพลวัตที่แท้จริงของข้อมูล ซึ่งมีอิทธิพลต่อการออกแบบมาตรการรับมือกับช่องทางลับด้วยเช่นกัน

การประมวลผลแบบขนานขนาดใหญ่ มัลติเธรด และเวกเตอร์: ผลกระทบต่อความปลอดภัยแบบไร้นาฬิกา

โปรเซสเซอร์สมัยใหม่มุ่งเน้นเพิ่มประสิทธิภาพไม่เพียงแค่การเพิ่มความเร็วสัญญาณนาฬิกาเท่านั้น แต่ยังรวมถึงการประมวลผลแบบขนานมากขึ้นด้วย ซึ่งเกี่ยวข้องกับคอร์หลายตัว การประมวลผลแบบมัลติเธรดด้วยฮาร์ดแวร์ และอื่นๆ หน่วยประมวลผลเวกเตอร์ที่สามารถประมวลผลจุดข้อมูลหลายจุดต่อคำสั่งเดียวนอกจากนี้ยังมีการพัฒนาตัวเร่งความเร็วเฉพาะทาง เช่น GPU, DSP หรือ TPU อีกด้วย

จากมุมมองด้านความปลอดภัย บล็อกการประมวลผลใหม่แต่ละบล็อกและระดับการประมวลผลแบบขนานใหม่แต่ละระดับ ถือเป็นพื้นที่ที่ต้องป้องกันเพิ่มเติม การประสานงานจึงเป็นสิ่งจำเป็น ความสอดคล้องของแคช การจัดการหน่วยความจำที่ใช้ร่วมกันกลไกการกีดกันร่วมกัน และหลีกเลี่ยงสภาวะการแข่งขันและการรั่วไหลของข้อมูลระหว่างเธรดหรือกระบวนการที่ทำงานพร้อมกัน

ในสภาพแวดล้อมที่ไม่มีนาฬิกาหรือแบบไฮบริด การประสานงานนี้จะอาศัยโปรโตคอลการสื่อสารระหว่างบล็อกมากกว่ารอบนาฬิกาสากล ตัวอย่างเช่น เคอร์เนลอาจใช้ สัญญาณของการร้องขอและการรับรู้ เพื่อเข้าถึงหน่วยความจำหรือทรัพยากรที่ใช้ร่วมกัน และความล่าช้าที่เกิดขึ้นจริงจะขึ้นอยู่กับปริมาณการรับส่งข้อมูลจริงในขณะนั้น ไม่ใช่จำนวนรอบการทำงานที่กำหนดไว้ตายตัว

พฤติกรรมนี้ เมื่อมองจากภายนอก ทำให้การโจมตีบางประเภทที่อาศัยการวัดเวลาที่แม่นยำมากโดยอิงจากจำนวนรอบการทำงานของนาฬิกาทำได้ยาก แต่ในขณะเดียวกัน นักออกแบบระบบรักษาความปลอดภัยก็ต้องก้าวข้ามการนับรอบการทำงานและอาศัย... ตัวนับเหตุการณ์ การวัดปริมาณการจราจร การใช้พลังงาน และสัญญาณอื่นๆ ที่ใช้ตรวจจับพฤติกรรมที่น่าสงสัย

ด้วยเหตุนี้ ผู้ผลิตหลายรายจึงรวมตัวนับประสิทธิภาพฮาร์ดแวร์ไว้ด้วย ซึ่งช่วยให้สามารถตรวจสอบสิ่งต่างๆ ได้แบบเรียลไทม์ เช่น การพลาดแคช การคาดการณ์สาขาที่ล้มเหลว การเข้าถึงหน่วยความจำเฉพาะ ฯลฯ เมื่อใช้งานอย่างถูกต้อง ตัวนับเหล่านี้จะเป็นเครื่องมือที่มีประสิทธิภาพสำหรับการเพิ่มประสิทธิภาพและ... ค้นหารูปแบบที่ผิดปกติ ลักษณะเฉพาะของ มัลแวร์ หรือการโจมตีขั้นสูง แม้แต่ในสถาปัตยกรรมแบบอะซิงโครนัสบางส่วนก็ตาม

การจำลองเสมือน, vCPU และการแยกส่วนในสภาพแวดล้อมสมัยใหม่

อีกหนึ่งองค์ประกอบสำคัญในภูมิทัศน์ปัจจุบันคือการจำลองเสมือน (virtualization) ในระบบคลาวด์ เราทำงานร่วมกับสิ่งต่างๆ อยู่ตลอดเวลา ซีพียูเสมือน (vCPU)ซึ่งเป็นส่วนย่อยเชิงตรรกะของความสามารถในการประมวลผลที่จัดสรรให้กับ เครื่องเสมือน หรือคอนเทนเนอร์บนฮาร์ดแวร์ทางกายภาพที่ใช้ร่วมกัน

แต่ละ vCPU นั้นโดยพื้นฐานแล้วคือชุดของเธรดหรือเวลาในการประมวลผลที่ไฮเปอร์ไวเซอร์จัดสรรให้กับคอร์ทางกายภาพ เพื่อให้การทำงานนี้เป็นไปอย่างราบรื่น CPU ทางกายภาพจะต้องมีทรัพยากรที่เหมาะสม โหมดพิเศษที่มีสิทธิพิเศษ ซึ่งช่วยให้ไฮเปอร์ไวเซอร์สามารถสร้างและแยกส่วนได้ เครื่องเสมือนดักจับคำสั่งสำคัญบางอย่าง และจัดการหน่วยความจำของแขกแต่ละคนโดยที่พวกเขาไม่สามารถแทรกแซงหรือสอดแนมซึ่งกันและกันได้

ในบริบทนี้ การรักษาความปลอดภัยแบบไร้สัญญาณนาฬิกาหมายความว่า การจัดสรรเวลา CPU ระหว่างเครื่องเสมือนไม่ได้ขึ้นอยู่กับสัญญาณนาฬิกาที่เป็นมาตรฐานเพียงอย่างเดียว แต่ยังขึ้นอยู่กับปัจจัยอื่นๆ อีกด้วย กลไกการวางแผนที่ยืดหยุ่นมากขึ้น โดยได้รับการสนับสนุนจากฮาร์ดแวร์ ไฮเปอร์ไวเซอร์ยังคงมองเห็นรอบการทำงานของนาฬิกา แต่การแปลงรอบการทำงานเหล่านั้นให้เป็นการทำงานที่มีประสิทธิภาพบนแต่ละคอร์นั้นสามารถเปลี่ยนแปลงได้โดยบล็อกแบบอะซิงโครนัสภายใน

จากมุมมองด้านความปลอดภัย นี่จึงจำเป็นต้องมีการออกแบบเครื่องมือตรวจสอบที่ไม่เพียงแต่จะนับจำนวนรอบการทำงานเท่านั้น แต่ยังต้องสามารถตีความตัวนับประสิทธิภาพ สถิติการใช้งาน และเหตุการณ์ระดับต่ำได้ด้วย ตรวจจับการใช้ทรัพยากรอย่างไม่เหมาะสม การหลุดออกจากเครื่องเสมือน หรือรูปแบบที่ผิดปกติ ซึ่งบ่งชี้ถึงการบุกรุก

นอกจากนี้ ในสภาพแวดล้อมที่ต้องใช้การประมวลผลอย่างหนัก ซึ่งมีการใช้หน่วยประมวลผลเวกเตอร์ หน่วยประมวลผลกราฟิก (GPU) และตัวเร่งความเร็วอื่นๆ อย่างเต็มที่ ผู้จัดการด้านความปลอดภัยต้องพิจารณาว่าบล็อกเหล่านี้ ไม่ว่าจะเป็นแบบซิงโครนัสหรืออะซิงโครนัส สามารถกลายเป็นเครื่องมือสำหรับ... เร่งการโจมตีทางด้านคริปโต ขุดคริปโตเคอร์เรนซีโดยที่ผู้ใช้ไม่รู้ตัว หรือทำการวิเคราะห์ข้อมูลที่ถูกขโมยในปริมาณมาก

ประสิทธิภาพ การใช้พลังงาน และการโอเวอร์คล็อก เมื่อเทียบกับการออกแบบที่ไม่มีนาฬิกา

สุดท้ายนี้ เราต้องพิจารณาความสัมพันธ์ระหว่างประสิทธิภาพและการใช้พลังงาน การเพิ่มความถี่สัญญาณนาฬิกาผ่านการโอเวอร์คล็อก (ตัวอย่างเช่น โดยการดำเนินการ...) การทดสอบความเสถียรด้วย OCCT) อนุญาตให้ CPU ดำเนินการได้มากขึ้นต่อวินาทีอย่างไรก็ตาม วิธีนี้จะทำให้สิ้นเปลืองพลังงานและอุณหภูมิสูงขึ้นอย่างมาก ในความเป็นจริง โปรเซสเซอร์รุ่นปัจจุบันหลายตัวสามารถปรับความถี่และแรงดันไฟฟ้าได้โดยอัตโนมัติตามภาระงานและอุณหภูมิภายในอยู่แล้ว

การออกแบบแบบอะซิงโครนัสเสนอทางเลือกใหม่: แทนที่จะใช้สัญญาณนาฬิกาที่เร็วมากและพยายามรักษาให้ทุกอย่างอยู่ในเฟสเดียวกัน พวกเขาปล่อยให้แต่ละส่วนทำงานตามจังหวะที่กำหนดโดยข้อมูลในช่วงที่มีภาระงานต่ำ ชิ้นส่วนที่ไม่ทำงานแทบจะไม่เปลี่ยนแปลงสถานะ ซึ่งช่วยลดการใช้พลังงานโดยไม่จำเป็นต้องใช้กลไกการจัดการพลังงานที่ซับซ้อนซึ่งอาศัยสัญญาณนาฬิกา

จากมุมมองด้านความปลอดภัย การใช้พลังงานและความร้อนที่ลดลง ไม่ใช่แค่เรื่องสิ่งแวดล้อมหรือค่าไฟฟ้าเท่านั้น แต่ยังหมายความว่า... ลดภาระให้กับชิ้นส่วนต่างๆลดโอกาสการเกิดความล้มเหลวอันเนื่องมาจากการเคลื่อนย้ายอิเล็กตรอนหรือการรั่วไหลของกระแสไฟฟ้า และอาจลดความเสี่ยงต่อการถูกโจมตีที่พยายามใช้ประโยชน์จากพฤติกรรมของระบบภายใต้สภาวะอุณหภูมิหรือแรงดันไฟฟ้าสูง

อย่างไรก็ตาม การออกแบบระบบที่ทำงานแบบอะซิงโครนัสได้อย่างสมบูรณ์และปลอดภัยนั้นไม่ใช่เรื่องง่าย ต้องมีการตรวจสอบอย่างเข้มงวดเกี่ยวกับโปรโตคอลการสื่อสารระหว่างบล็อก สภาวะการแข่งขัน และสถานะระหว่างกลาง เพื่อป้องกันข้อผิดพลาด พฤติกรรมที่ไม่แน่นอนซึ่งผู้โจมตีสามารถใช้ประโยชน์ได้ความซับซ้อนของการออกแบบ การขาดแคลนเครื่องมือที่พัฒนาแล้ว และความจำเป็นในการรักษาความเข้ากันได้กับซอฟต์แวร์ที่มีอยู่เดิม ส่งผลให้ในขณะนี้ โปรเซสเซอร์เชิงพาณิชย์ส่วนใหญ่ยังคงทำงานแบบซิงโครนัสเป็นหลัก โดยมีส่วนที่ทำงานแบบอะซิงโครนัสขนาดเล็กอยู่บ้าง

การรวมกันของปัจจัยทั้งหมดเหล่านี้—สถาปัตยกรรมภายใน การจัดการนาฬิกา การประมวลผลแบบขนาน การจำลองเสมือน และพลังงาน—ทำให้การรักษาความปลอดภัยในสภาพแวดล้อมที่ไม่มีนาฬิกาสากลเป็นเรื่องที่ต้องพิจารณาอย่างรอบคอบ การออกแบบแบบอะซิงโครนัสช่วยลดการโจมตีที่อาศัยเวลาบางประเภทและอำนวยความสะดวกในการใช้กลยุทธ์การประหยัดพลังงานที่มีประสิทธิภาพสูง แต่ก็ยังนำมาซึ่งความท้าทายใหม่ๆ ในการตรวจสอบ การตรวจสอบบัญชี และการยืนยันพฤติกรรมของฮาร์ดแวร์ ดังนั้นกุญแจสำคัญจึงอยู่ที่การบูรณาการ กลไกการสังเกตการณ์และการแยกส่วนที่มีประสิทธิภาพ ตั้งแต่ชิปซิลิคอนไปจนถึงซอฟต์แวร์ระดับสูงสุด

นักเขียนผู้หลงใหลเกี่ยวกับโลกแห่งไบต์และเทคโนโลยีโดยทั่วไป ฉันชอบแบ่งปันความรู้ผ่านการเขียน และนั่นคือสิ่งที่ฉันจะทำในบล็อกนี้ เพื่อแสดงให้คุณเห็นสิ่งที่น่าสนใจที่สุดเกี่ยวกับอุปกรณ์ ซอฟต์แวร์ ฮาร์ดแวร์ แนวโน้มทางเทคโนโลยี และอื่นๆ เป้าหมายของฉันคือการช่วยคุณนำทางโลกดิจิทัลด้วยวิธีที่เรียบง่ายและสนุกสนาน