- Klokkeløs sikkerhet er relatert til asynkrone CPU-design, der avhengigheten av en global klokke reduseres eller elimineres.

- Moderne prosessorer kombinerer hurtigbuffere, MMU-er, parallellisme og flere tråder, noe som kompliserer både ytelse og sikkerhet.

- Klokkeløse design kan redusere tidsangrep, men de krever nye former for overvåking og revisjon. maskinvare.

- Virtualisering, vCPU-er og spesialiserte akseleratorer utvider angrepsflaten, noe som gjør det viktig å integrere sikkerhet fra silisiumnivå.

Expression Klokkeløs sikkerhet høres ut som et futuristisk konsept.Men det er faktisk tett knyttet til hvordan nåværende prosessorer og systemer er designet og beskyttet. For å forstå det ordentlig, må vi dykke ned i hvordan en CPU fungerer internt, hvordan instruksjonsutførelse er organisert, og hvilken rolle det berømte klokkesignalet spiller i å sette tempoet for hele systemet.

I de siste tiårene har prosessorer vært i et kappløp om å øke hastigheten sin. klokkefrekvens, integrere flere transistorer og multiplisere parallellismen deresSamtidig har det dukket opp design som forsøker å bryte fri fra avhengigheten av den globale klokken, enten på tvers av hele brikken eller i bestemte deler. Dette området, det med asynkrone eller klokkeløse design, åpner for svært interessante muligheter når det gjelder strømforbruk og varmespredning ... og også spesifikke sikkerhetsutfordringer som ofte grupperes under konseptet klokkeløs sikkerhet.

CPU-en som systemets sentrum og dens forhold til klokken

Når vi snakker om klokkerelatert sikkerhet, er det første vi må huske nøyaktig hva en CPU er. I hovedsak Den sentrale prosessorenheten er hjernen i datamaskinen.: komponenten som tolker og utfører programinstruksjoner, koordinerer minne, input/output og spesialiserte koprosessorer som GPU-er.

Innenfor en moderne CPU finner vi flere distinkte blokker. På den ene siden er det aritmetisk logisk enhet (ALU)Den aritmetiske logikkenheten (ALU) er ansvarlig for matematiske og logiske operasjoner med heltall. Så har vi registrene, som er små, ultrasnelle minner der dataene prosessoren jobber med lagres. Og i tillegg til alt dette er det en kontrollenhet som bestemmer, syklus for syklus, hva som skal gjøres, hva som skal leses fra minnet og hva som skal skrives.

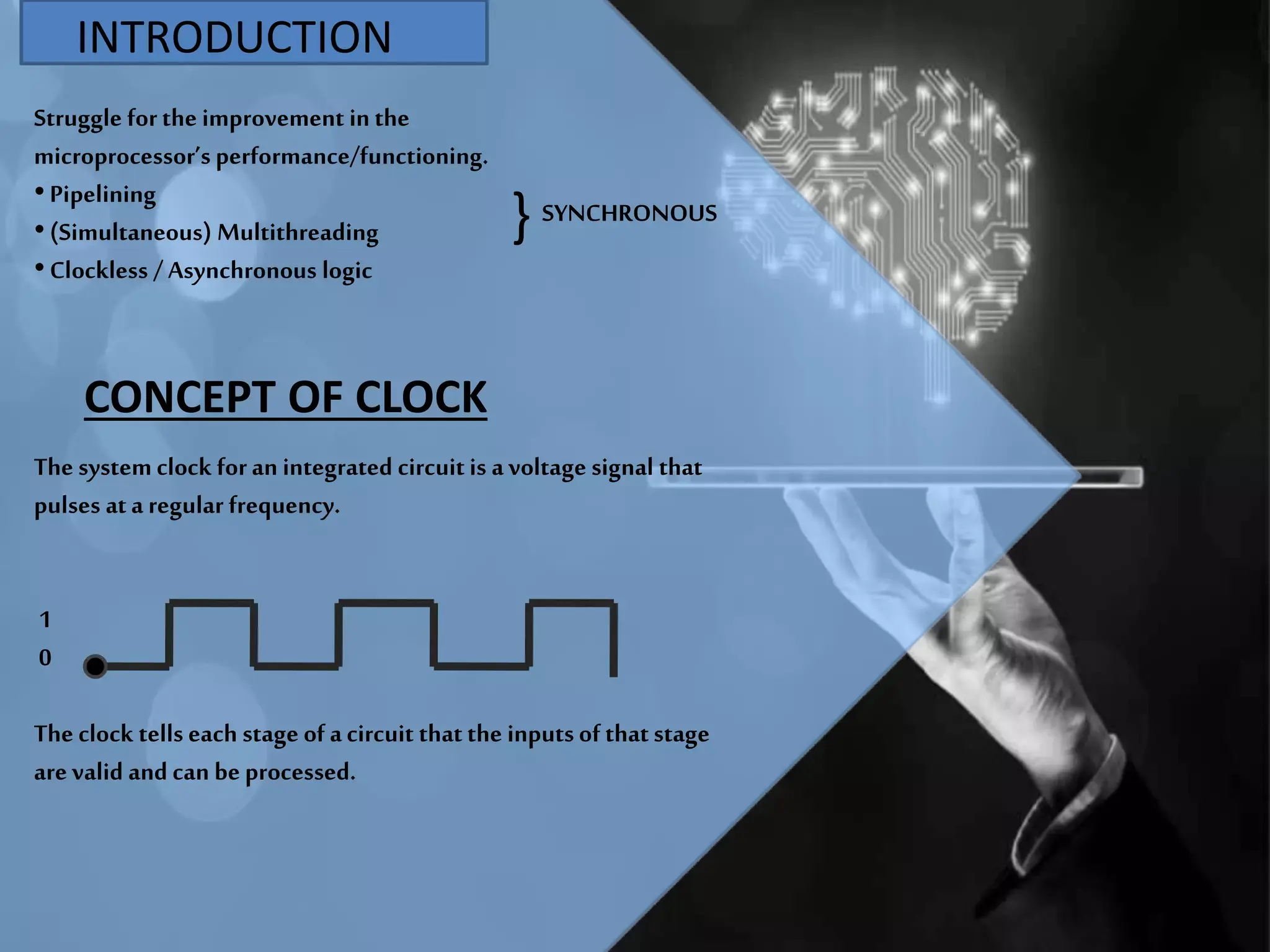

De fleste moderne prosessorer er synkrone design. Dette betyr at alle disse interne blokkene er koordinert ved hjelp av en periodisk klokkesignalen slags elektronisk metronom som angir utførelsestempoet. Hvert tikk på denne klokken går ett trinn fremover i den såkalte instruksjonssyklusen: instruksjonen hentes, dekodes, utføres, resultatene lagres, og syklusen begynner på nytt.

I en tradisjonell prosessor genereres klokken av en ekstern oscillator som sender millioner eller milliarder av pulser per sekund. Frekvensen til disse pulsene, målt i hertz, megahertz eller gigahertz, forteller oss hvor mange «tikk» CPU-en har tilgjengelig hvert sekund for å flytte data og utføre operasjoner. Jo høyere klokkefrekvens, desto mer potensielt arbeid per sekund.forutsatt at resten av arkitekturen utfyller den.

Dermed avhenger ytelsen ikke bare av klokken, men også av hvor mange instruksjoner per syklus (IPC) Den er i stand til å fullføre prosessoren. Frekvens-til-IPC-produktet gir oss en idé om millionene av instruksjoner per sekund den kan utføre, selv om teoretiske tall vanligvis er mye mer optimistiske enn det som faktisk sees med virkelige programmer.

Fra fast kabling til integrerte mikroprosessorer

For å sette klokkeløse design i kontekst, er det nyttig å se på hvordan CPU-en har utviklet seg. Tidlige elektroniske datamaskiner, som ENIAC, var kablede maskiner med fast programFor å endre oppgaver måtte systemet fysisk kobles om. Den revolusjonerende ideen var den lagrede programdatamaskinen, der instruksjonene ligger i minnet; prosessoren leser og utfører dem ganske enkelt.

Den lagrede programarkitekturen assosiert med John von Neumann vant til slutt frem. I den, Instruksjoner og data deler samme minneplassI motsetning til Harvard-arkitektur, som fysisk skiller begge typer informasjon, følger nesten alle generelle CPU-er i dag en von Neumann-arkitektur, selv om mange rene eller hybride Harvard-prosessorer fortsatt eksisterer i den innebygde verdenen.

De første prosessorene ble bygget med reléer eller vakuumrør. De var klumpete, trege og hadde en pålitelighet svært begrenset. Spranget til faststofftransistoren på 50- og 60-tallet tillot øke hastigheten radikalt og redusere forbruk og størrelseDerfra gikk overgangen fra diskrete kretser til integrerte kretser (IC-er), der flere og flere transistorer ble satt sammen på én brikke.

Med fremveksten av den integrerte kretsen, først liten skala (SSI), deretter mellomstor skala (MSI), stor skala (LSI) og til slutt veldig stor skala (VLSI), ble CPU-en komprimert til den passet alt på én eller noen få brikkerDenne integrasjonen kulminerte i mikroprosessoren, der hele prosessorenheten er produsert på én silisiumbrikke.

El Intel 4004Intel 8080, som ble lansert i 1971, var en av de første kommersielle mikroprosessorene. Kraftigere design fulgte snart, som Intel 8080, som ble grunnlaget for personlige datamaskiner. Fra det tidspunktet ble begrepet CPU nesten alltid brukt for å referere til disse mikroprosessorene.

Viktige interne komponenter i en moderne CPU

Moderne CPUer bruker en stor del av silisiumoverflaten sin til hjelpeelementer designet for for å få mest mulig ut av hver klokkesyklusFor eksempel har nesten alle prosessorer flere nivåer av hurtigbuffer: små, men veldig raske minner plassert i nærheten av kjernene som lagrer kopier av de mest brukte dataene, slik at de ikke trenger å stadig ha tilgang til RAM-en.

I tillegg til L1-, L2- og ofte L3-hurtigbufferne, inkluderer en kompleks CPU en minnehåndteringsenhet (MMU) som oversetter virtuelle adresser (de som håndteres av operativsystemet) til fysiske adresser i RAM, administrerer virtuelt minne og gir isolasjon mellom prosesser.

I beregningsplanet har vi flere spesialiserte utførelsesenheter: ALU for heltall, flyttallsenhet (FPU) For desimaloperasjoner brukes adressegenereringsenheter (AGU-er) til raskt å beregne minneplasseringer, og i mange arkitekturer brukes vektorenheter eller SIMD-er til å operere på flere datapunkter samtidig.

Det finnes også en kontrollenhet, som kan være fastkoblet logikk eller mikrokodebasert, det vil si en internt program som oversetter hver instruksjon på høyt nivå i en sekvens av interne kontrollsignaler. I mange prosessorer kan denne mikrokoden oppdateres, noe som muliggjør korrigering av designfeil eller justering av virkemåte i etterkant.

Til slutt finnes det et batteri av interne registre: generelle registre, akkumulatorer, programtellere, statusregistre med flagg som indikerer ting som om resultatet av en operasjon er null, negativt eller har produsert et overløp, osv. Alt dette koordineres etter den klassiske løkken. opptak, dekoding og utførelse av instruksjoner.

Slik kjører du et program trinn for trinn

Den grunnleggende operasjonen til enhver CPU koker ned til å hente instruksjoner fra minnet og behandle dem etter hverandre. Dette skjer i tre hovedfaser. Først, fasen av fange (hente), der instruksjonen hvis adressering er gitt av programtelleren leses fra minnet.

Deretter kommer dekodingsfasen. Den nylig innhentede instruksjonen går gjennom en binær dekoder som undersøker operasjonskoden (opcode) og oversetter det bitmønsteret til konkrete signaler som aktiverer eller deaktiverer deler av prosessoren. Det er der det avgjøres om det er et tillegg, et hopp, en lasting fra minnet osv., og hvilke registre eller adresser som er involvert.

Til slutt utføres operasjonen. ALU-en eller den tilhørende enheten utfører beregningen eller dataflyten, og resultatet lagres vanligvis i et register eller i minnet. Hvis programflyten må endres, for eksempel med et betinget hopp, oppdateres programtelleren med en ny adresse. Det settet med instruksjoner, data og hopp Det er den som ender opp med å danne løkker, funksjoner, betingelser og all logikken i programmene våre.

I enkle prosessorer skjer alt lineært og sekvensielt. Men i moderne CPUer Mange av disse stadiene overlappes ved bruk av parallellismeteknikkerMålet er at hver klokkesyklus skal gjøre så mye arbeid som mulig, og at maskinvaren ikke skal være inaktiv.

Parallelisme, kanalisering og utførelse i feil rekkefølge

For å unngå å kaste bort klokken, introduserte designerne rørledningerDatabanen er delt inn i flere stadier, på samme måte som et samlebånd. Mens én instruksjon dekodes, hentes den neste allerede fra minnet, og enda en annen kan kjøres i ALU-en.

Problemet er at noen ganger trenger én instruksjon resultatet av en annen som ikke er ferdig ennå. Dette skaper dataavhengigheter og tvinger frem introduksjonen av bobler eller ventetider i pipelinen. For å minimere disse forsinkelsene brukes teknikker som operandvideresending, forgreningsprediksjon og senere, feilaktig utførelse, der prosessoren internt omordner instruksjonene så lenge programmets endelige resultat respekteres.

Neste trinn var superskalar design: å utstyre prosessoren med flere utførelsesenheter av samme type for å kunne gi flere instruksjoner per klokkesyklusforutsatt at det ikke er noen konflikter mellom dem. En intern koordinator analyserer instruksjonsflyten, oppdager hva som kan utføres parallelt og fordeler dem mellom de forskjellige enhetene.

Alle disse Triks De er inkludert i den såkalte instruksjonsparallellisme (ILP)De praktiske begrensningene ved disse teknikkene og den økende vanskeligheten med å øke klokkehastighetene ytterligere uten å øke strømforbruket og varmen betydelig, medførte at produsentene på et visst tidspunkt også begynte å investere i... parallellisme på oppgavenivåflere tråder og flere kjerner per brikke (og mekanismer som parkering for kjerner).

Slik blir de født flerkjernede prosessorer og arkitekturer med maskinvare-multitråding, der hver kjerne kan opprettholde tilstanden til flere utførelsestråder og raskt bytte mellom dem for å bedre utnytte interne ressurser mens noen tråder venter på data fra minnet.

Klokkefrekvensens rolle og dens fysiske grenser

Når vi går tilbake til klokken, er det viktig å merke seg at signalet som synkroniserer prosessoren til syvende og sist er et elektrisk signal som forplanter seg gjennom brikkenEtter hvert som frekvensene øker og antallet transistorer vokser, blir det svært vanskelig å opprettholde signalet perfekt justert overalt. Klokkefordeling, faseforskyvninger og signalintegritetsproblemer oppstår.

På den annen side fører hver klokkeovergang til at en rekke transistorer endrer tilstand, selv om et bestemt område av prosessoren ikke gjør noe nyttig i det øyeblikket. Dette oversettes til energiforbruk og varmeavledning rett og slett for å holde metronomen i gang. For å lindre dette ble teknikker som klokkestyring introdusert, som selektivt slår av klokkesignalet i ubrukte blokker, noe som reduserer energiforbruket.

Men utover en viss terskel slutter det å være rimelig å øke frekvensen: problemer med forbruk, temperatur og klokkefordeling skyter i været. Den flaskehalsen Dette er en av grunnene til at ideen om å kvitte seg, helt eller delvis, med en global klokke har blitt utforsket: det er her asynkrone eller «klokkeløse» design kommer inn i bildet.

I et asynkront design, i stedet for å ha en enkelt klokke som markerer tiden for hele brikken, Det er dataene og kontrollsignalene i seg selv som synkroniserer operasjoneneBlokkene kommuniserer ved hjelp av forespørsels- og bekreftelsesprotokoller (håndtrykk): når dataene er klare, varsler produsenten forbrukeren, og forbrukeren reagerer uten å vente på en fast klokkekant.

De har blitt bygget fullstendig asynkrone prosessorer Kompatibel med kjente instruksjonssett, som den ARM-baserte AMULET-familien eller MIPS-avledede prosjekter. Det finnes også hybriddesign, der bare visse enheter (for eksempel en spesifikk ALU) opererer uten en global klokke, mens resten av prosessoren forblir synkron.

Hva mener vi med klokkeløs sikkerhet?

Når man snakker om klokkeløs sikkerhet, blandes to ideer: på den ene siden asynkron design som teknikk for å redusere forbruk og varmePå den annen side er det implikasjonen av å kvitte seg med klokken når man analyserer, overvåker og beskytter systemets oppførsel mot angrep eller feil.

I synkrone systemer er mange sikkerhets- og overvåkingsverktøy avhengige av eksistensen av en stabil og forutsigbar tidsrytmeDet er relativt enkelt å telle sykluser, måle hvor lang tid en bestemt operasjon tar, eller prøve å oppdage unormal oppførsel ved å måle variasjoner i tider som skal være konstante.

I et asynkront eller delvis klokkeløst system blir disse rigide tidsreferansene utvannet. Utførelsestiden for en operasjon kan avhenge av den faktiske tilgjengeligheten av data, overbelastning på visse interne ruter eller mindre fysiske variasjoner. Fra en angripers perspektiv kan dette gjøre vanskeligere å montere tidsbaserte sidekanalangrepfordi den globale klokken som fungerer som en felles referanse forsvinner.

Denne samme dynamiske naturen kompliserer imidlertid også saken for alle som ønsker å observere og revidere systemet internt. Mange prober og maskinvaretellere er designet for å operere basert på klokkesykluser; uten en tydelig global klokke, måle ytelse og oppdage mistenkelig aktivitet Det krever da andre målinger og mekanismer.

Videre tillater den asynkrone designen, ved å være frigjort fra klokken, at databaner aktiveres på litt forskjellige tidspunkter i hver utførelse, noe som potensielt randomiserer midlertidige lekkasjer Men det kan også åpne andre dører, for eksempel i form av forskjellige og mer komplekse energiforbruksmønstre som kan utnyttes av effektanalyseangrep.

Datarepresentasjon, ordstørrelse og sikkerhet

En annen viktig faktor knyttet til CPU-arkitektur er hvordan den representerer og håndterer data. Nesten alle moderne prosessorer bruker binær representasjon, med spenningsverdier som tilsvarer 0 og 1. Ordstørrelsen (8, 16, 32, 64 bits…) bestemmer området for heltall som kan håndteres direkte og mengden adresserbart minne.

Fra et sikkerhetssynspunkt påvirker ordstørrelsen adresserommet og sannsynligheten for kollisjoner, overløp og pekerfeilEt 32-bits system med 2^32 mulige adresser har svært klare begrensninger sammenlignet med et 64-bits system. Dessuten er mange moderne beskyttelsesmekanismer, som visse beskyttede minneutvidelser, avhengige av å ha et stort adresserom.

Bruken av MMU og adresseoversettelse introduserer også et ekstra lag mellom programmet og det fysiske minnet, noe som er avgjørende for isolere prosesserImplementer virtuelt minne og beskytt kjernen. I asynkrone sammenhenger må koordineringen mellom disse oversettelsene og håndsignalene mellom klokkeløse blokker være svært godt utformet for å unngå å skape sikkerhetshull eller kappløpsforhold.

Vektorutvidelser (SIMD) og flyttallsenheter tillater igjen å jobbe med store datamengder parallelt. Dette er et tveegget sverd: på den ene siden, Det akselererer kryptografiske algoritmer og analyseoppgaver.På den annen side, hvis den utnyttes ondsinnet, gir den en stor datakapasitet til å knekke svake chiffer eller iverksette brute-force-angrep.

I et klokkeløst eller delvis asynkront scenario må måten disse parallelle databehandlingsenhetene programmeres og beskyttes på, ta hensyn til at Utførelses- og forbruksmønstre følger ikke lenger en fast rytme diktert av klokken.men vil reagere på dataenes reelle dynamikk, som også påvirker utformingen av mottiltak mot sidekanaler.

Massiv parallellisme, flertråding og vektorer: innvirkning på klokkeløs sikkerhet

Moderne prosessorer tar sikte på å øke ytelsen ikke bare ved å øke klokkehastigheten, men også ved å kjøre mer arbeid parallelt. Dette involverer flere kjerner, multitråding av maskinvare og Vektorenheter som er i stand til å behandle flere datapunkter per instruksjonI tillegg til alt dette kommer fremveksten av spesifikke akseleratorer som GPU-er, DSP-er eller TPU-er.

Fra et sikkerhetsperspektiv er hver nye utførelsesblokk og hvert nytt nivå av parallellisme en ekstra overflate å beskytte. Koordinering er nødvendig. hurtigbufferkonsistens, administrasjon av delt minne, gjensidige ekskluderingsmekanismer og unngå kappløpsbetingelser og informasjonslekkasjer mellom tråder eller samtidige prosesser.

I klokkeløse eller hybride miljøer er denne koordineringen mer avhengig av kommunikasjonsprotokoller mellom blokker enn av globale klokkesykluser. For eksempel kan en kjerne bruke signaler om forespørsel og gjenkjenning for å få tilgang til minne eller en delt ressurs, og den effektive forsinkelsen vil avhenge av den faktiske trafikken på det tidspunktet, ikke av et fast antall sykluser.

Denne oppførselen, sett utenfra, gjør visse angrep som er avhengige av svært presise tidsmålinger basert på antall klokkesykluser vanskelige. Men samtidig må sikkerhetsdesignere gå utover syklustelling og stole på... hendelsestellere, trafikkmåling, energiforbruk og andre tegn for å oppdage mistenkelig oppførsel.

Derfor integrerer mange produsenter ytelsestellere for maskinvare, som tillater sanntidsovervåking av ting som hurtigbufferfeil, mislykkede grenprediksjoner, spesifikk minnetilgang osv. Når de brukes riktig, er disse tellerne et kraftig verktøy for både å optimalisere ytelse og... finn uregelmessige mønstre karakteristisk for malware eller avanserte utnyttelser, selv i delvis asynkrone arkitekturer.

Virtualisering, vCPU og isolasjon i moderne miljøer

En annen viktig ingrediens i dagens landskap er virtualisering. I skyen jobber vi kontinuerlig med Virtuelle CPU-er (vCPU), som er logiske fragmenter av prosesseringskapasitet allokert til virtuelle maskiner eller containere oppå delt fysisk maskinvare.

Hver vCPU er i hovedsak et sett med tråder eller utførelsestider som hypervisoren planlegger på de fysiske kjernene. For at dette skal fungere bra, tilbyr den fysiske CPU-en spesielle privilegerte moduser som lar hypervisorer opprette og isolere virtuelle maskiner, avlytte visse sensitive instruksjoner og administrere minnet til hver gjest uten at de kan forstyrre eller spionere på hverandre.

I denne sammenhengen innebærer klokkeløs sikkerhet at tildelingen av CPU-tid mellom virtuelle maskiner ikke bare avhenger av en ensartet klokke, men også av mer dynamiske planleggingsmekanismer støttes av maskinvaren. Hypervisoren ser fortsatt klokkesykluser, men hvordan disse syklusene konverteres til effektivt arbeid på hver kjerne kan endres av interne asynkrone blokker.

Fra et sikkerhetssynspunkt nødvendiggjør dette design av overvåkingsverktøy som ikke bare teller antall tellere, men som også kan tolke ytelsestellere, bruksstatistikk og hendelser på lavt nivå. oppdage ressursmisbruk, virtuelle maskinrømminger eller uregelmessige mønstre som peker på et innbrudd.

I dataintensive miljøer, der vektorenheter, GPU-er og andre akseleratorer utnyttes fullt, må sikkerhetsansvarlige dessuten vurdere at disse blokkene, enten de er synkrone eller asynkrone, kan bli verktøy for akselerere kryptoangrep, utvinning av kryptovalutaer bak brukerens rygg eller utføre analyser av store mengder stjålne data.

Ytelse, strømforbruk og overklokking kontra et design uten klokke

Til slutt må vi vurdere forholdet mellom ytelse og strømforbruk. Å øke klokkefrekvensen gjennom overklokking (for eksempel ved å utføre en Stabilitetstest med OCCT) tillater en CPU utføre flere operasjoner per sekundDette øker imidlertid strømforbruket og temperaturen betydelig. Faktisk justerer mange nåværende prosessorer allerede dynamisk frekvens og spenning basert på arbeidsbelastning og intern temperatur.

Asynkrone design tilbyr et alternativ: i stedet for å bruke en veldig rask klokke og prøve å holde alt i fase, De lar hver blokk fungere i det tempoet som dataene dikterer.I perioder med lav belastning endrer inaktive deler knapt tilstand, noe som reduserer forbruket uten behov for komplekse klokkebaserte strømstyringsmekanismer.

Fra et sikkerhetsperspektiv er mindre forbruk og mindre varme ikke bare et miljøproblem eller et spørsmål om strømregninger. Det betyr også mindre belastning på komponentene, mindre sannsynlighet for feil forårsaket av elektromigrasjon eller strømlekkasje, og potensielt mindre eksponering for angrep som forsøker å utnytte systemets oppførsel under ekstreme temperatur- eller spenningsforhold.

Det er imidlertid ikke trivielt å designe et fullstendig asynkront og sikkert system. Det krever svært grundig verifisering av kommunikasjonsprotokoller mellom blokker, kappløpsbetingelser og mellomliggende tilstander for å forhindre feil. ikke-deterministisk atferd som kan utnyttes av en angriperDesignets kompleksitet, mangelen på modne verktøy og behovet for bakoverkompatibilitet med eksisterende programvare har medført at de fleste kommersielle prosessorer foreløpig stort sett forblir synkrone med små asynkrone øyer.

Kombinasjonen av alle disse faktorene – intern arkitektur, klokkehåndtering, parallellisme, virtualisering og strømforbruk – gjør sikkerhet i miljøer uten global klokke til en delikat balansegang. Asynkrone design reduserer visse tidsbaserte angrep og legger til rette for svært raffinerte strømsparingsstrategier, men de presenterer også nye utfordringer for overvåking, revisjon og verifisering av maskinvareatferd, så nøkkelen ligger i integrasjon. robuste observerbarhets- og isolasjonsmekanismer fra selve silisiumet til programvare på høyeste nivå.

Lidenskapelig forfatter om verden av bytes og teknologi generelt. Jeg elsker å dele kunnskapen min gjennom å skrive, og det er det jeg skal gjøre i denne bloggen, vise deg alle de mest interessante tingene om dingser, programvare, maskinvare, teknologiske trender og mer. Målet mitt er å hjelpe deg med å navigere i den digitale verden på en enkel og underholdende måte.