- La sicurezza senza clock riguarda i progetti di CPU asincrone, in cui la dipendenza da un clock globale viene ridotta o eliminata.

- I processori moderni combinano cache, MMU, parallelismo e thread multipli, il che complica sia le prestazioni che la sicurezza.

- I progetti senza clock possono mitigare gli attacchi temporali, ma richiedono nuove forme di monitoraggio e audit. hardware.

- La virtualizzazione, le vCPU e gli acceleratori specializzati ampliano la superficie di attacco, rendendo essenziale integrare la sicurezza a livello di silicio.

L'espressione La sicurezza senza orologio sembra un concetto futuristico.Ma in realtà è strettamente legato al modo in cui i processori e i sistemi attuali sono progettati e protetti. Per comprenderlo appieno, dobbiamo approfondire il funzionamento interno di una CPU, come è organizzata l'esecuzione delle istruzioni e quale ruolo gioca il famoso segnale di clock nel dettare il ritmo dell'intero sistema.

Negli ultimi decenni, i processori sono stati impegnati in una corsa per aumentare la loro velocità. frequenza di clock, integrare più transistor e moltiplicare il loro parallelismoAllo stesso tempo, sono emersi progetti che tentano di liberarsi dalla dipendenza dal clock globale, sia per l'intero chip che per parti specifiche. Quest'area, quella dei progetti asincroni o senza clock, apre opportunità molto interessanti in termini di consumo energetico e dissipazione del calore... e anche sfide specifiche per la sicurezza che vengono spesso raggruppate sotto il concetto di sicurezza senza clock.

La CPU come centro del sistema e la sua relazione con l'orologio

Quando parliamo di sicurezza legata agli orologi, la prima cosa da ricordare è esattamente cos'è una CPU. In sostanza, la L'unità di elaborazione centrale è il cervello del computer.: il componente che interpreta ed esegue le istruzioni del programma, coordina la memoria, l'input/output e i coprocessori specializzati come le GPU.

All'interno di una CPU moderna troviamo diversi blocchi distinti. Da un lato, c'è il unità aritmetico-logica (ALU)L'unità aritmetico-logica (ALU) è responsabile delle operazioni matematiche e logiche con i numeri interi. Poi ci sono i registri, piccole memorie ultraveloci in cui vengono memorizzati i dati con cui il processore sta elaborando. E, soprattutto, c'è un'unità di controllo che decide, ciclo dopo ciclo, cosa fare, cosa leggere dalla memoria e cosa scrivere.

La maggior parte dei processori moderni sono progetti sincroni. Ciò significa che tutti quei blocchi interni sono coordinati utilizzando un segnale di orologio periodicouna sorta di metronomo elettronico che scandisce il ritmo dell'esecuzione. Ogni ticchettio di questo orologio fa avanzare di un passo il cosiddetto ciclo di istruzioni: l'istruzione viene recuperata, decodificata, eseguita, i risultati vengono memorizzati e il ciclo ricomincia.

In un processore tradizionale, il clock è generato da un oscillatore esterno che invia milioni o miliardi di impulsi al secondo. La frequenza di questi impulsi, misurata in hertz, megahertz o gigahertz, ci dice quanti "tick" la CPU ha a disposizione ogni secondo per spostare dati ed eseguire operazioni. Maggiore è la frequenza di clock, maggiore è il lavoro potenziale al secondo.a condizione che il resto dell'architettura lo completi.

Quindi, le prestazioni dipendono non solo dall'orologio, ma anche da quanti istruzioni per ciclo (IPC) È in grado di completare il processore. Il prodotto frequenza-IPC ci dà un'idea dei milioni di istruzioni al secondo che può eseguire, sebbene i dati teorici siano solitamente molto più ottimistici di quanto effettivamente osservato con i programmi reali.

Dal cablaggio fisso ai microprocessori integrati

Per contestualizzare i progetti senza orologio, è utile esaminare l'evoluzione della CPU. I primi computer elettronici, come l'ENIAC, erano macchine cablate a programma fissoPer modificare le attività, il sistema doveva essere riprogrammato fisicamente. L'idea rivoluzionaria fu il computer a programma memorizzato, in cui le istruzioni risiedono in memoria; il processore si limita a leggerle ed eseguirle.

Alla fine prevalse l'architettura a programma memorizzato associata a John von Neumann. In essa, Istruzioni e dati condividono lo stesso spazio di memoriaA differenza dell'architettura Harvard, che separa fisicamente entrambi i tipi di informazioni, oggi quasi tutte le CPU generiche seguono un'architettura von Neumann, sebbene nel mondo embedded esistano ancora molti processori Harvard puri o ibridi.

I primi processori furono costruiti con relè o tubi a vuoto. Erano ingombranti, lenti e avevano un affidabilità molto limitato. Il passaggio al transistor a stato solido negli anni '50 e '60 ha permesso aumentare radicalmente la velocità e ridurre i consumi e le dimensioniDa lì si è passati dai circuiti discreti ai circuiti integrati (CI), inserendo sempre più transistor su un singolo chip.

Con l'avvento del circuito integrato, prima su piccola scala (SSI), poi su media scala (MSI), su larga scala (LSI) e infine su scala molto grande (VLSI), la CPU è stata compressa fino a quando non si adattava tutto su uno o pochi chipQuesta integrazione ha portato al microprocessore, in cui l'intera unità di elaborazione è realizzata su un singolo chip di silicio.

El Intel 4004L'Intel 8080, lanciato nel 1971, fu uno dei primi microprocessori commerciali. Seguirono presto modelli più potenti, come l'Intel 8080, che divenne il fondamento dei personal computer. Da quel momento in poi, il termine CPU fu quasi sempre utilizzato per riferirsi a questi microprocessori.

Componenti interni chiave di una CPU moderna

Le CPU moderne dedicano una grande porzione della loro superficie di silicio ad elementi ausiliari progettati per per ottenere il massimo da ogni ciclo di clockAd esempio, quasi tutti i processori incorporano diversi livelli di cache: piccole ma velocissime memorie situate vicino ai core che memorizzano copie dei dati più utilizzati, in modo da non dover accedere costantemente alla RAM.

Oltre alle cache L1, L2 e spesso L3, una CPU complessa include una unità di gestione della memoria (MMU) che traduce gli indirizzi virtuali (quelli gestiti dal sistema operativo) in indirizzi fisici nella RAM, gestisce la memoria virtuale e fornisce isolamento tra i processi.

Nel piano computazionale abbiamo diverse unità di esecuzione specializzate: l'ALU per gli interi, l' unità a virgola mobile (FPU) Per le operazioni decimali, vengono utilizzate unità di generazione di indirizzi (AGU) per calcolare rapidamente le posizioni di memoria e, in molte architetture, vengono utilizzate unità vettoriali o SIMD per operare su più punti dati contemporaneamente.

Esiste anche un'unità di controllo, che può essere logica cablata o basata su microcodice, ovvero un programma interno che traduce ogni istruzione di alto livello in una sequenza di segnali di controllo interni. In molti processori, questo microcodice può essere aggiornato, consentendo la correzione di errori di progettazione o l'adeguamento del comportamento a posteriori.

Infine, c'è una serie di registri interni: registri generici, accumulatori, contatori di programma, registri di stato con flag che indicano, ad esempio, se il risultato di un'operazione è zero, negativo o ha prodotto un overflow, ecc. Tutto questo è coordinato seguendo il classico ciclo. cattura, decodifica ed esecuzione delle istruzioni.

Come eseguire un programma passo dopo passo

Il funzionamento di base di qualsiasi CPU si riduce al recupero di istruzioni dalla memoria e alla loro elaborazione una dopo l'altra. Questo avviene in tre fasi principali. Innanzitutto, la fase di catturare (recuperare), in cui l'istruzione il cui indirizzamento è dato dal contatore di programma viene letta dalla memoria.

Segue la fase di decodifica. L'istruzione appena catturata passa attraverso un decodificatore binario che esamina il suo codice operativo (opcode) e traduce quel modello di bit in segnali concreti che abilitano o disabilitano parti del processore. È qui che si decide se si tratta di un'aggiunta, un salto, un caricamento dalla memoria, ecc. e quali registri o indirizzi sono coinvolti.

Infine, l'operazione viene eseguita. L'ALU o l'unità corrispondente esegue il calcolo o lo spostamento dei dati e il risultato viene solitamente memorizzato in un registro o in memoria. Se il flusso del programma deve essere modificato, ad esempio con un salto condizionato, il contatore di programma viene aggiornato con un nuovo indirizzo. Questo insieme di istruzioni, dati e salti È quello che finisce per formare cicli, funzioni, condizioni e tutta la logica dei nostri programmi.

Nei processori semplici, tutto avviene in modo lineare e sequenziale. Ma nelle CPU moderne Molte di queste fasi sono sovrapposte utilizzando tecniche di parallelismoL'obiettivo è che ogni ciclo di clock svolga più lavoro possibile e che l'hardware non resti inattivo.

Parallelismo, canalizzazione ed esecuzione fuori ordine

Per evitare di sprecare l'orologio, i progettisti hanno introdotto il conduttureIl percorso dei dati è suddiviso in diverse fasi, simili a una catena di montaggio. Mentre un'istruzione viene decodificata, la successiva viene già recuperata dalla memoria e un'altra ancora potrebbe essere in esecuzione nell'ALU.

Il problema è che a volte un'istruzione necessita del risultato di un'altra che non è ancora terminata. Questo crea dipendenze tra i dati e forza l'introduzione di bolle o attese nella pipeline. Per ridurre al minimo questi ritardi, tecniche come l'inoltro degli operandi, la predizione delle diramazioni e, più tardi, la esecuzione fuori servizio, in cui il processore riordina internamente le istruzioni purché venga rispettato il risultato finale del programma.

Il passo successivo è stato il design superscalare: dotare il processore di diverse unità di esecuzione dello stesso tipo per poter emettere più istruzioni per ciclo di clockA condizione che non vi siano conflitti tra di esse. Un dispatcher interno analizza il flusso di istruzioni, individua ciò che può essere eseguito in parallelo e lo distribuisce tra le diverse unità.

Tutti questi Tricks Sono compresi nel cosiddetto parallelismo didattico (ILP)I limiti pratici di queste tecniche e la crescente difficoltà di aumentare ulteriormente la velocità di clock senza aumentare significativamente il consumo di energia e il calore hanno fatto sì che, a un certo punto, anche i produttori abbiano iniziato a investire in... parallelismo a livello di attività: più thread e più core per chip (e meccanismi come il parcheggio per i nuclei).

Ecco come nascono processori multicore e architetture con multithreading hardware, in cui ogni core può mantenere lo stato di diversi thread di esecuzione e passare rapidamente da uno all'altro per sfruttare al meglio le risorse interne mentre alcuni thread attendono i dati dalla memoria.

Il ruolo della frequenza di clock e i suoi limiti fisici

Tornando all'orologio, è importante notare che il segnale che sincronizza il processore è, in definitiva, un segnale elettrico che si propaga attraverso il chipCon l'aumentare delle frequenze e del numero di transistor, mantenere il segnale perfettamente allineato diventa molto difficile. Si verificano problemi di distribuzione del clock, sfasamenti e integrità del segnale.

D'altra parte, ogni transizione di clock fa sì che numerosi transistor cambino stato, anche se una certa area del processore non sta facendo nulla di utile in quel momento. Questo si traduce in consumo di energia e dissipazione del calore semplicemente per mantenere il metronomo in funzione. Per ovviare a questo inconveniente, sono state introdotte tecniche come il clock gating, che disattiva selettivamente il segnale di clock nei blocchi non utilizzati, riducendo il consumo energetico.

Tuttavia, oltre una certa soglia, aumentare la frequenza non è più ragionevole: i problemi di consumo, temperatura e distribuzione del clock aumentano vertiginosamente. Quel collo di bottiglia Questo è uno dei motivi per cui è stata esplorata l'idea di rinunciare, totalmente o parzialmente, a un orologio globale: è qui che entrano in gioco i progetti asincroni o "clockless".

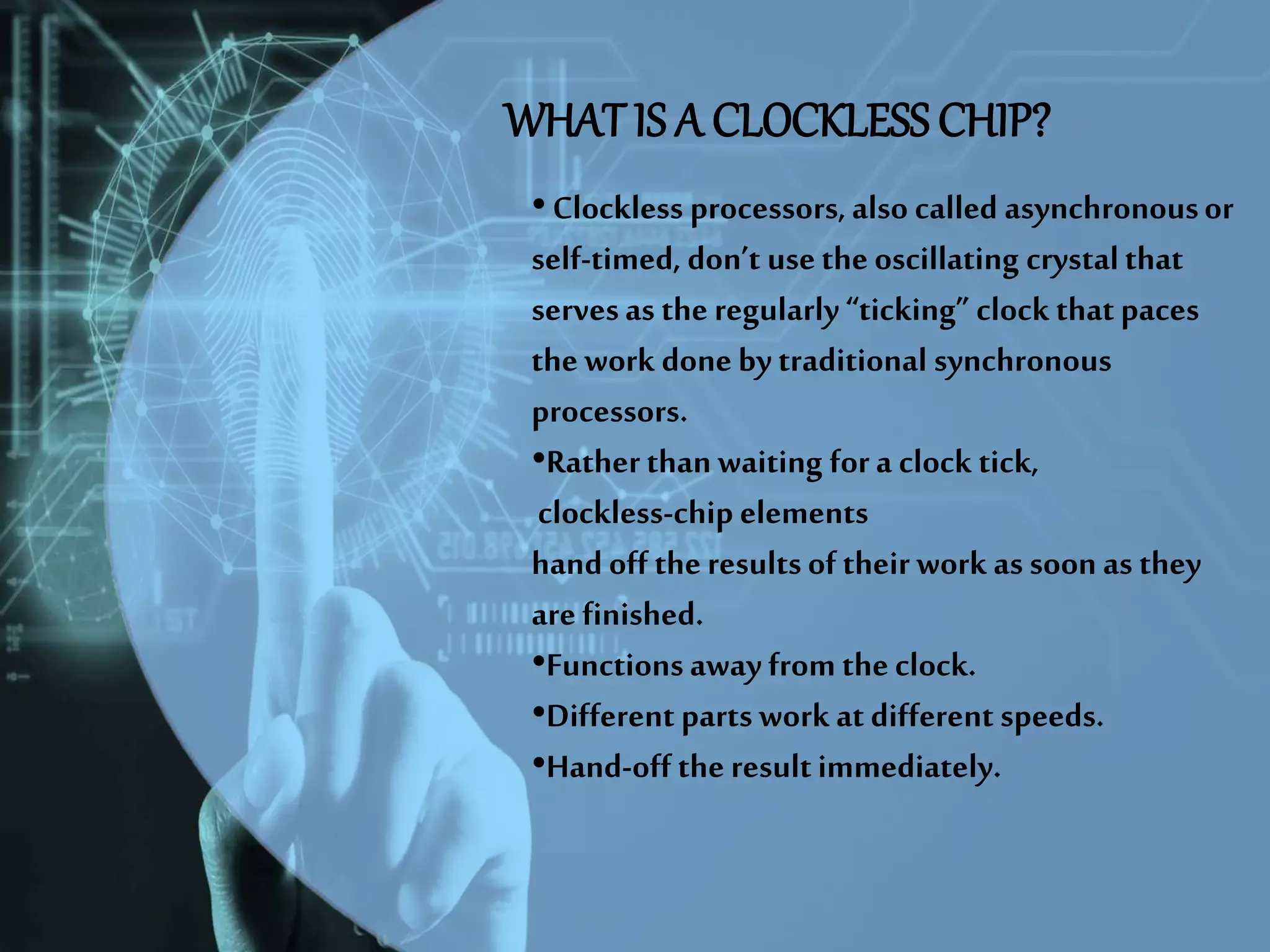

In un design asincrono, invece di avere un singolo orologio che segna il tempo per l'intero chip, Sono i dati e i segnali di controllo stessi che sincronizzano le operazioniI blocchi comunicano tramite protocolli di richiesta e di conferma (handshaking): quando i dati sono pronti, il produttore avvisa il consumatore, il quale reagisce senza attendere un fronte di clock fisso.

Sono stati costruiti processori completamente asincroni Compatibile con set di istruzioni noti, come la famiglia AMULET basata su ARM o progetti derivati da MIPS. Esistono anche progetti ibridi, in cui solo alcune unità (ad esempio, una specifica ALU) operano senza un clock globale, mentre il resto del processore rimane sincrono.

Cosa intendiamo per sicurezza senza orologio?

Quando si parla di sicurezza senza orologio, due idee sono confuse: da un lato, la progettazione asincrona come tecnica per ridurre i consumi e il caloreD'altro canto, ciò implica dover rinunciare all'orologio quando si analizza, si monitora e si protegge il comportamento del sistema da attacchi o guasti.

Nei sistemi sincroni, molti strumenti di sicurezza e monitoraggio si basano sull'esistenza di un ritmo temporale stabile e prevedibileÈ relativamente facile contare i cicli, misurare la durata di una determinata operazione o provare a rilevare comportamenti anomali misurando le variazioni in tempi che dovrebbero essere costanti.

In un sistema asincrono o parzialmente privo di clock, questi rigidi riferimenti temporali vengono diluiti. Il tempo di esecuzione di un'operazione può dipendere dall'effettiva disponibilità dei dati, dalla congestione su determinate rotte interne o da piccole variazioni fisiche. Dal punto di vista di un aggressore, questo può comportare più difficile montare attacchi side-channel basati sul timingperché l'orologio globale che funge da riferimento comune scompare.

Tuttavia, questa stessa natura dinamica complica anche le cose per chiunque voglia osservare e verificare il sistema internamente. Molte sonde e contatori hardware sono progettati per funzionare in base a cicli di clock; senza un clock globale chiaro, misurare le prestazioni e rilevare attività sospette Richiede poi altre metriche e meccanismi.

Inoltre, il design asincrono, essendo liberato dal clock, consente ai percorsi dati di essere attivati in momenti leggermente diversi in ogni esecuzione, il che potenzialmente randomizza le perdite temporanee Ma potrebbe anche aprire altre porte, ad esempio sotto forma di modelli di consumo energetico diversi e più complessi che potrebbero essere sfruttati da attacchi di analisi della potenza.

Rappresentazione dei dati, dimensione delle parole e sicurezza

Un altro fattore importante legato all'architettura della CPU è il modo in cui rappresenta e gestisce i dati. Quasi tutti i processori moderni utilizzano rappresentazione binaria, con valori di tensione corrispondenti a 0 e 1. La dimensione della parola (8, 16, 32, 64 bit…) determina l'intervallo di interi che possono essere gestiti direttamente e la quantità di memoria indirizzabile.

Dal punto di vista della sicurezza, la dimensione della parola influisce sullo spazio degli indirizzi e sulla probabilità di collisioni, overflow ed errori di puntatoreUn sistema a 32 bit con 2^32 possibili indirizzi presenta limitazioni molto evidenti rispetto a un sistema a 64 bit. Inoltre, molti meccanismi di protezione moderni, come alcune estensioni di memoria protetta, si basano su un ampio spazio di indirizzamento.

L'uso della MMU e della traduzione degli indirizzi introduce anche un ulteriore livello tra il programma e la memoria fisica, qualcosa di cruciale per isolare i processiImplementare la memoria virtuale e proteggere il kernel. In contesti asincroni, il coordinamento tra queste traduzioni e i segnali manuali tra blocchi senza clock deve essere progettato molto bene per evitare la creazione di falle di sicurezza o condizioni di competizione.

A loro volta, le estensioni vettoriali (SIMD) e le unità in virgola mobile consentono di lavorare con grandi volumi di dati in parallelo. Questa è un'arma a doppio taglio: da un lato, Accelera gli algoritmi crittografici e le attività di analisi.D'altro canto, se sfruttato in modo dannoso, fornisce una grande capacità di calcolo per decifrare cifrari deboli o lanciare attacchi brute-force.

In uno scenario senza clock o parzialmente asincrono, il modo in cui queste unità di elaborazione parallela sono programmate e protette deve tenere conto del fatto che I modelli di esecuzione e di consumo non seguono più un ritmo fisso dettato dall'orologio.ma risponderà alla dinamica reale dei dati, che influenza anche la progettazione di contromisure contro i canali laterali.

Parallelismo massiccio, multithreading e vettori: impatto sulla sicurezza senza clock

I processori moderni mirano ad aumentare le prestazioni non solo aumentando la velocità di clock, ma anche eseguendo più processi in parallelo. Ciò implica più core, multithreading hardware e unità vettoriali in grado di elaborare più punti dati per istruzioneA tutto questo si aggiunge l'ascesa di acceleratori specifici come GPU, DSP o TPU.

Dal punto di vista della sicurezza, ogni nuovo blocco di esecuzione e ogni nuovo livello di parallelismo rappresentano un'ulteriore superficie da proteggere. Il coordinamento è necessario. coerenza della cache, gestione della memoria condivisa, meccanismi di esclusione reciproca ed evitare condizioni di competizione e perdite di informazioni tra thread o processi concorrenti.

In ambienti senza clock o ibridi, questo coordinamento si basa maggiormente sui protocolli di comunicazione tra i blocchi che sui cicli di clock globali. Ad esempio, un kernel potrebbe utilizzare segnali di richiesta e riconoscimento per accedere alla memoria o a una risorsa condivisa e il ritardo effettivo dipenderà dal traffico effettivo in quel momento, non da un numero fisso di cicli.

Questo comportamento, visto dall'esterno, rende difficili alcuni attacchi che si basano su misurazioni temporali molto precise basate sul numero di cicli di clock. Ma allo stesso tempo, i progettisti della sicurezza devono andare oltre il conteggio dei cicli e affidarsi a... contatori di eventi, misurazione del traffico, consumo energetico e altri segnali per rilevare comportamenti sospetti.

Ecco perché molti produttori integrano contatori delle prestazioni hardware, che consentono il monitoraggio in tempo reale di fattori quali mancate cache, previsioni di diramazioni non riuscite, accessi specifici alla memoria, ecc. Se utilizzati correttamente, questi contatori sono uno strumento potente sia per ottimizzare le prestazioni che... trovare modelli anomali caratteristica di il malware o exploit avanzati, anche in architetture parzialmente asincrone.

Virtualizzazione, vCPU e isolamento negli ambienti moderni

Un altro ingrediente chiave nel panorama odierno è la virtualizzazione. Nel cloud, lavoriamo costantemente con CPU virtuali (vCPU), che sono frammenti logici di capacità di elaborazione allocata a Macchine virtuali o contenitori su hardware fisico condiviso.

Ogni vCPU è essenzialmente un insieme di thread o tempi di esecuzione che l'hypervisor pianifica sui core fisici. Affinché questo funzioni correttamente, la CPU fisica offre modalità privilegiate speciali che consentono agli hypervisor di creare e isolare Macchine virtuali, intercettare alcune istruzioni sensibili e gestire la memoria di ogni ospite senza che questi possano interferire o spiarsi a vicenda.

In questo contesto, la sicurezza senza clock implica che l'allocazione del tempo di CPU tra macchine virtuali dipende non solo da un clock uniforme, ma anche da meccanismi di pianificazione più dinamici supportato dall'hardware. L'hypervisor continua a rilevare i cicli di clock, ma il modo in cui tali cicli vengono convertiti in lavoro effettivo su ciascun core può essere modificato tramite blocchi asincroni interni.

Dal punto di vista della sicurezza, ciò richiede la progettazione di strumenti di monitoraggio che non si limitino a contare i tick, ma siano anche in grado di interpretare contatori delle prestazioni, statistiche di utilizzo ed eventi di basso livello. rilevare abusi di risorse, fughe di macchine virtuali o modelli irregolari che indicano un'intrusione.

Inoltre, negli ambienti ad alta intensità di calcolo, in cui le unità vettoriali, le GPU e altri acceleratori sono pienamente utilizzati, i responsabili della sicurezza devono considerare che questi blocchi, sincroni o asincroni, possono diventare strumenti per accelerare gli attacchi crittografici, estrazione di criptovalute alle spalle dell'utente o eseguire analisi di grandi volumi di dati rubati.

Prestazioni, consumo energetico e overclocking rispetto a un design senza clock

Infine, dobbiamo considerare il rapporto tra prestazioni e consumo energetico. Aumentare la frequenza di clock tramite overclocking (ad esempio, eseguendo un Test di stabilità con OCCT) consente una CPU eseguire più operazioni al secondoTuttavia, questo aumenta significativamente il consumo energetico e la temperatura. Infatti, molti processori attuali regolano già dinamicamente frequenza e tensione in base al carico di lavoro e alla temperatura interna.

I progetti asincroni offrono un'alternativa: invece di utilizzare un clock molto veloce e cercare di mantenere tutto in fase, Lasciano che ogni blocco funzioni al ritmo dettato dai dati.Nei periodi di basso carico, le parti inattive cambiano stato a malapena, riducendo il consumo senza la necessità di complessi meccanismi di gestione dell'alimentazione basati sull'orologio.

Dal punto di vista della sicurezza, meno consumi e meno calore non sono solo una questione ambientale o una questione di bollette elettriche. Significano anche meno stress sui componenti, minore probabilità di guasti indotti da elettromigrazione o dispersione di corrente e potenzialmente minore esposizione ad attacchi che tentano di sfruttare il comportamento del sistema in condizioni estreme di temperatura o tensione.

Tuttavia, progettare un sistema completamente asincrono e sicuro non è un'impresa banale. Richiede una verifica molto rigorosa dei protocolli di comunicazione tra blocchi, delle condizioni di gara e degli stati intermedi per prevenire errori. comportamenti non deterministici che possono essere sfruttati da un aggressoreLa complessità della progettazione, la scarsità di strumenti maturi e la necessità di compatibilità con i software esistenti hanno fatto sì che, per il momento, la maggior parte dei processori commerciali rimanga prevalentemente sincrona, con piccole isole asincrone.

La combinazione di tutti questi fattori – architettura interna, gestione del clock, parallelismo, virtualizzazione e alimentazione – rende la sicurezza in ambienti privi di un clock globale un delicato equilibrio. Le progettazioni asincrone mitigano alcuni attacchi basati sulla temporizzazione e facilitano strategie di risparmio energetico altamente raffinate, ma presentano anche nuove sfide per il monitoraggio, l'audit e la verifica del comportamento dell'hardware, quindi la chiave sta nell'integrazione. meccanismi robusti di osservabilità e isolamento dal silicio stesso al software di livello più elevato.

Scrittore appassionato del mondo dei byte e della tecnologia in generale. Adoro condividere le mie conoscenze attraverso la scrittura, ed è quello che farò in questo blog, mostrarti tutte le cose più interessanti su gadget, software, hardware, tendenze tecnologiche e altro ancora. Il mio obiettivo è aiutarti a navigare nel mondo digitale in modo semplice e divertente.