- Keamanan tanpa jam (clockless security) berkaitan dengan desain CPU asinkron, di mana ketergantungan pada jam global dikurangi atau dihilangkan.

- Prosesor modern menggabungkan cache, MMU, paralelisme, dan banyak thread, yang memperumit kinerja dan keamanan.

- Desain tanpa jam dapat mengurangi serangan waktu, tetapi memerlukan bentuk pemantauan dan audit baru. perangkat keras.

- Virtualisasi, vCPU, dan akselerator khusus memperluas permukaan serangan, sehingga sangat penting untuk mengintegrasikan keamanan dari tingkat silikon.

La Expresion Keamanan tanpa jam terdengar seperti konsep futuristik.Namun sebenarnya hal ini terkait erat dengan bagaimana prosesor dan sistem saat ini dirancang dan dilindungi. Untuk memahaminya dengan benar, kita perlu mempelajari cara kerja CPU secara internal, bagaimana eksekusi instruksi diatur, dan peran apa yang dimainkan oleh sinyal clock yang terkenal dalam mengatur kecepatan seluruh sistem.

Dalam beberapa dekade terakhir, prosesor telah berlomba-lomba untuk meningkatkan kecepatannya. frekuensi clock, mengintegrasikan lebih banyak transistor dan melipatgandakan paralelismenyaPada saat yang sama, muncul desain yang berupaya melepaskan diri dari ketergantungan pada clock global, baik di seluruh chip maupun di bagian-bagian tertentu. Bidang ini, yaitu desain asinkron atau tanpa clock, membuka peluang yang sangat menarik dalam hal konsumsi daya dan pembuangan panas… dan juga tantangan keamanan spesifik yang sering dikelompokkan di bawah konsep keamanan tanpa clock.

CPU sebagai pusat sistem dan hubungannya dengan jam.

Ketika kita berbicara tentang keamanan terkait jam tangan, hal pertama yang perlu diingat adalah apa sebenarnya CPU itu. Pada dasarnya, Unit pemrosesan pusat adalah otak dari komputer.: komponen yang menerjemahkan dan mengeksekusi instruksi program, mengkoordinasikan memori, input/output, dan koprosesor khusus seperti GPU.

Di dalam CPU modern, kita menemukan beberapa blok yang berbeda. Di satu sisi, terdapat... unit logika aritmatika (ALU)Unit aritmatika logika (ALU) bertanggung jawab atas operasi matematika dan logika dengan bilangan bulat. Kemudian ada register, yaitu memori kecil dan sangat cepat tempat data yang sedang diproses oleh prosesor disimpan. Dan di atas semuanya, ada unit kontrol yang memutuskan, siklus demi siklus, apa yang harus dilakukan, apa yang harus dibaca dari memori, dan apa yang harus ditulis.

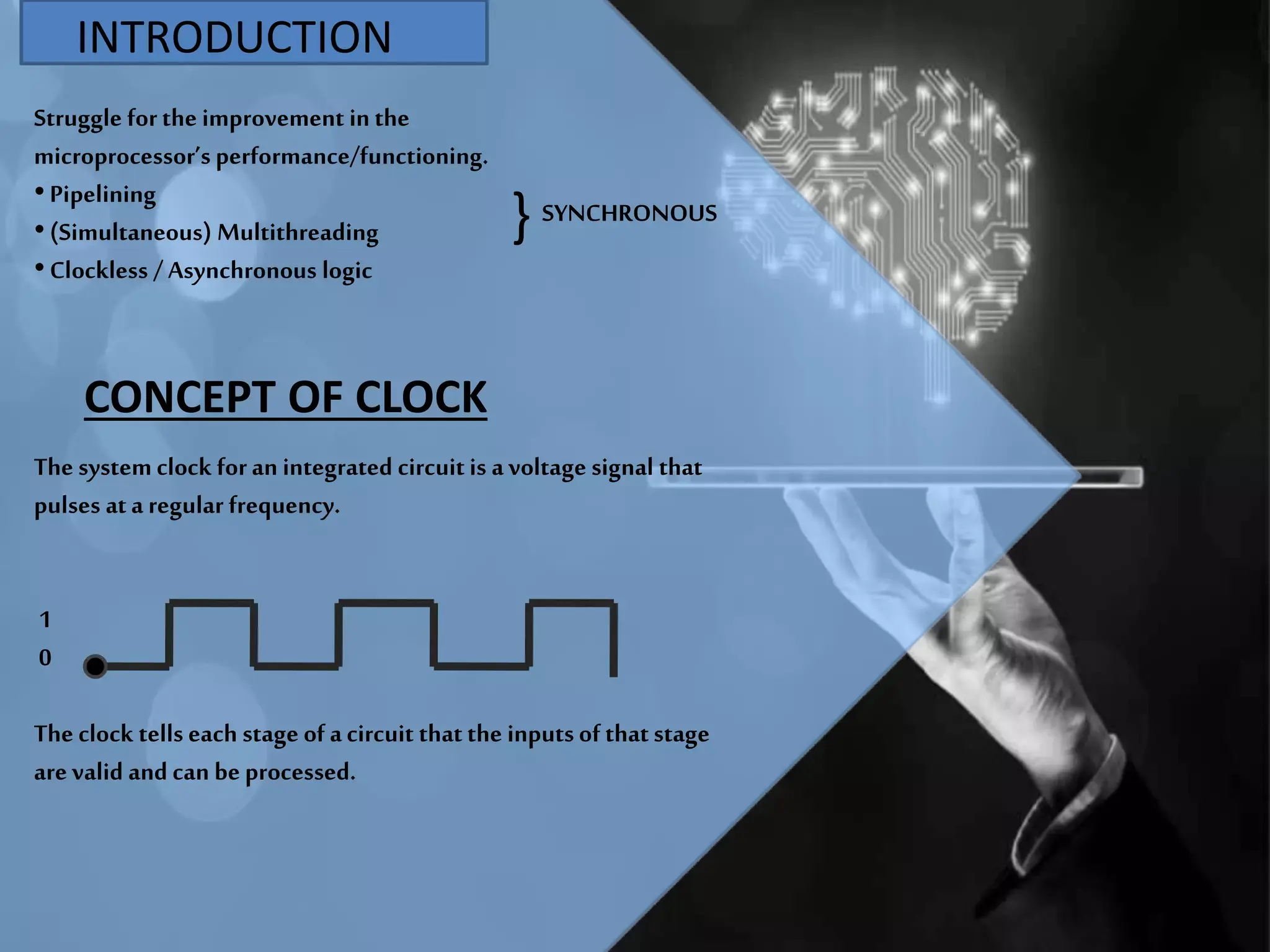

Sebagian besar prosesor modern menggunakan desain sinkron. Ini berarti bahwa semua blok internal tersebut dikoordinasikan menggunakan suatu mekanisme. sinyal jam periodikSejenis metronom elektronik yang mengatur kecepatan eksekusi. Setiap detak jam ini memajukan satu langkah dari apa yang disebut siklus instruksi: instruksi diambil, didekode, dieksekusi, hasilnya disimpan, dan siklus dimulai lagi.

Pada prosesor tradisional, clock dihasilkan oleh osilator eksternal yang mengirimkan jutaan atau miliaran pulsa per detik. Frekuensi pulsa ini, yang diukur dalam hertz, megahertz, atau gigahertz, memberi tahu kita berapa banyak "tick" yang tersedia bagi CPU setiap detik untuk memindahkan data dan melakukan operasi. Semakin tinggi frekuensi clock, semakin besar potensi kerja per detik.asalkan bagian arsitektur lainnya melengkapinya.

Dengan demikian, kinerja tidak hanya bergantung pada kecepatan clock, tetapi juga pada berapa banyak instruksi per siklus (IPC) Ia mampu melengkapi prosesor. Produk frekuensi-ke-IPC memberi kita gambaran tentang jutaan instruksi per detik yang dapat dieksekusinya, meskipun angka teoretis biasanya jauh lebih optimis daripada apa yang sebenarnya terlihat pada program nyata.

Dari pengkabelan tetap hingga mikroprosesor terintegrasi

Untuk memahami konteks desain tanpa jam, ada baiknya meninjau bagaimana CPU telah berevolusi. Komputer elektronik awal, seperti ENIAC, mesin program tetap berkabelUntuk mengubah tugas, sistem harus diubah susunan kabelnya secara fisik. Ide revolusioner tersebut adalah komputer program tersimpan, di mana instruksi berada di memori; prosesor hanya membaca dan mengeksekusinya.

Arsitektur program tersimpan yang dikaitkan dengan John von Neumann akhirnya berhasil. Di dalamnya, Instruksi dan data berbagi ruang memori yang sama.Berbeda dengan arsitektur Harvard, yang secara fisik memisahkan kedua jenis informasi, saat ini hampir semua CPU tujuan umum mengikuti arsitektur von Neumann, meskipun banyak prosesor Harvard murni atau hibrida masih ada di dunia sistem tertanam.

Prosesor pertama dibangun dengan menggunakan relai atau tabung vakum. Prosesor tersebut berukuran besar, lambat, dan memiliki keandalan sangat terbatas. Lompatan ke transistor solid-state pada tahun 50-an dan 60-an memungkinkan Meningkatkan kecepatan secara drastis serta mengurangi konsumsi dan ukuran.Dari situ, terjadilah transisi dari sirkuit diskrit ke sirkuit terpadu (IC), dengan menempatkan semakin banyak transistor pada satu chip.

Dengan munculnya sirkuit terpadu, pertama skala kecil (SSI), kemudian skala menengah (MSI), skala besar (LSI), dan akhirnya skala sangat besar (VLSI), CPU dikompresi hingga sesuai dengan ukuran perangkat. semuanya pada satu atau beberapa chipIntegrasi ini berpuncak pada mikroprosesor, di mana seluruh unit pemrosesan diproduksi pada satu keping silikon tunggal.

El Intel 4004Intel 8080, yang dirilis pada tahun 1971, adalah salah satu mikroprosesor komersial pertama. Desain yang lebih canggih segera menyusul, seperti Intel 8080, yang menjadi dasar komputer pribadi. Sejak saat itu, istilah CPU hampir selalu digunakan untuk merujuk pada mikroprosesor ini.

Komponen internal utama dari CPU modern

CPU modern mengalokasikan sebagian besar permukaan silikonnya untuk elemen tambahan yang dirancang untuk untuk mendapatkan hasil maksimal dari setiap siklus jam.Sebagai contoh, hampir setiap prosesor menggabungkan beberapa tingkat cache: memori kecil namun sangat cepat yang terletak di dekat inti prosesor yang menyimpan salinan data yang paling sering digunakan sehingga prosesor tidak perlu terus-menerus mengakses RAM.

Selain cache L1, L2, dan seringkali L3, CPU yang kompleks juga mencakup unit manajemen memori (MMU) yang menerjemahkan alamat virtual (yang ditangani oleh sistem operasi) menjadi alamat fisik di RAM, mengelola memori virtual dan menyediakan isolasi antar proses.

Dalam bidang komputasi, kita memiliki beberapa unit eksekusi khusus: ALU untuk bilangan bulat, unit titik mengambang (FPU) Untuk operasi desimal, unit pembangkit alamat (AGU) digunakan untuk menghitung lokasi memori dengan cepat, dan di banyak arsitektur, unit vektor atau SIMD digunakan untuk beroperasi pada beberapa titik data secara bersamaan.

Terdapat juga unit kontrol, yang dapat berupa logika kabel atau berbasis mikrokode, yaitu, sebuah program internal yang menerjemahkan setiap instruksi tingkat tinggi dalam serangkaian sinyal kontrol internal. Pada banyak prosesor, mikrokode ini dapat diperbarui, memungkinkan koreksi kesalahan desain atau penyesuaian perilaku setelahnya.

Terakhir, terdapat serangkaian register internal: register serbaguna, akumulator, penghitung program, register status dengan flag yang menunjukkan hal-hal seperti apakah hasil suatu operasi adalah nol, negatif, atau telah menghasilkan overflow, dll. Semua ini dikoordinasikan mengikuti loop klasik. menangkap, mendekode, dan mengeksekusi instruksi..

Cara menjalankan program langkah demi langkah

Prinsip dasar pengoperasian CPU pada dasarnya adalah mengambil instruksi dari memori dan memprosesnya satu per satu. Proses ini terjadi dalam tiga fase utama. Pertama, tahap... tangkap (ambil), di mana instruksi yang pengalamatannya diberikan oleh penghitung program dibaca dari memori.

Selanjutnya adalah fase dekoding. Instruksi yang baru ditangkap melewati dekoder biner yang memeriksa kode operasinya (opcode) dan menerjemahkan pola bit tersebut menjadi sinyal konkret yang mengaktifkan atau menonaktifkan bagian-bagian prosesor. Di situlah diputuskan apakah itu operasi penambahan, lompatan, pemuatan dari memori, dan lain sebagainya, serta register atau alamat mana yang terlibat.

Akhirnya, operasi dieksekusi. ALU atau unit yang sesuai melakukan perhitungan atau perpindahan data, dan hasilnya biasanya disimpan dalam register atau memori. Jika alur program perlu diubah, misalnya dengan lompatan bersyarat, penghitung program diperbarui dengan alamat baru. Kumpulan tersebut instruksi, data, dan lompatan Dialah yang pada akhirnya membentuk perulangan, fungsi, kondisi, dan semua logika program kita.

Pada prosesor sederhana, semuanya terjadi secara linier dan berurutan. Namun pada CPU modern... Banyak dari tahapan ini saling tumpang tindih menggunakan teknik paralelisme.Tujuannya adalah agar setiap siklus clock melakukan pekerjaan sebanyak mungkin, dan agar perangkat keras tidak menganggur.

Paralelisme, penyaluran, dan eksekusi di luar urutan

Untuk menghindari pemborosan jam tangan, para desainer memperkenalkan perpipaanJalur data dibagi menjadi beberapa tahap, mirip dengan jalur perakitan. Sementara satu instruksi sedang diuraikan, instruksi berikutnya sudah diambil dari memori, dan instruksi lain mungkin sedang dieksekusi di ALU.

Masalahnya adalah terkadang satu instruksi membutuhkan hasil dari instruksi lain yang belum selesai. Hal ini menciptakan ketergantungan data dan memaksa munculnya gelembung atau penundaan dalam pipeline. Untuk meminimalkan penundaan ini, teknik seperti penerusan operan, prediksi percabangan, dan kemudian, eksekusi di luar urutan, di mana prosesor secara internal menyusun ulang instruksi selama hasil akhir program tetap dihormati.

Langkah selanjutnya adalah desain superscalar: melengkapi prosesor dengan beberapa unit eksekusi dari jenis yang sama agar mampu mengeluarkan beberapa instruksi per siklus clockasalkan tidak ada konflik di antara mereka. Sebuah pengatur internal menganalisis alur instruksi, mendeteksi apa yang dapat dieksekusi secara paralel, dan mendistribusikannya di antara berbagai unit.

Semua ini Trik Mereka termasuk dalam apa yang disebut paralelisme instruksional (ILP)Keterbatasan praktis dari teknik-teknik ini dan semakin sulitnya meningkatkan kecepatan clock tanpa meningkatkan konsumsi daya dan panas secara signifikan menyebabkan, pada titik tertentu, para produsen juga mulai berinvestasi dalam... paralelisme tingkat tugas: beberapa thread dan beberapa core per chip (dan mekanisme seperti parkir untuk inti).

Beginilah cara mereka dilahirkan prosesor multicore dan arsitektur dengan multithreading perangkat keras, di mana setiap inti dapat mempertahankan status beberapa thread eksekusi dan dengan cepat beralih di antara mereka untuk memanfaatkan sumber daya internal dengan lebih baik sementara beberapa thread menunggu data dari memori.

Peran frekuensi jam dan batasan fisiknya

Kembali ke soal jam, penting untuk dicatat bahwa sinyal yang menyinkronkan prosesor pada akhirnya adalah sebuah sinyal listrik yang merambat melalui chipSeiring meningkatnya frekuensi dan bertambahnya jumlah transistor, menjaga agar sinyal tetap selaras sempurna menjadi sangat sulit. Masalah distribusi clock, pergeseran fasa, dan integritas sinyal pun muncul.

Di sisi lain, setiap transisi clock menyebabkan banyak transistor berubah status, bahkan jika area tertentu dari prosesor tidak melakukan sesuatu yang berguna pada saat itu. Hal ini diterjemahkan menjadi konsumsi energi dan pembuangan panas Sederhananya, tujuannya adalah agar metronom tetap berjalan. Untuk mengatasi hal ini, diperkenalkan teknik seperti clock gating, yang secara selektif mematikan sinyal clock pada blok yang tidak digunakan, sehingga mengurangi konsumsi energi.

Namun, di luar ambang batas tertentu, meningkatkan frekuensi menjadi tidak masuk akal: masalah konsumsi daya, suhu, dan distribusi clock meningkat drastis. Hambatan itu Inilah salah satu alasan mengapa gagasan untuk menghilangkan, sepenuhnya atau sebagian, jam global telah dieksplorasi: di sinilah desain asinkron atau "tanpa jam" berperan.

Dalam desain asinkron, alih-alih memiliki satu jam tunggal yang menandai el tiempo untuk seluruh chip, Data dan sinyal kontrol itulah yang menyinkronkan operasi.Blok-blok tersebut berkomunikasi menggunakan protokol permintaan dan pengakuan (jabat tangan): ketika data siap, produsen memberi tahu konsumen, dan konsumen bereaksi tanpa menunggu tepi jam yang tetap.

Mereka telah dibangun prosesor asinkron penuh Kompatibel dengan set instruksi yang sudah dikenal, seperti keluarga AMULET berbasis ARM atau proyek-proyek turunan MIPS. Terdapat juga desain hibrida, di mana hanya unit-unit tertentu (misalnya, ALU tertentu) yang beroperasi tanpa jam global, sementara bagian prosesor lainnya tetap sinkron.

Apa yang kami maksud dengan keamanan tanpa jam?

Ketika berbicara tentang keamanan tanpa jam, dua gagasan dicampuradukkan: di satu sisi, desain asinkron sebagai teknik untuk mengurangi konsumsi dan panasDi sisi lain, terdapat implikasi dari mengabaikan jam ketika menganalisis, memantau, dan melindungi perilaku sistem dari serangan atau kegagalan.

Dalam sistem sinkron, banyak alat keamanan dan pemantauan bergantung pada keberadaan suatu ritme temporal yang stabil dan dapat diprediksiMenghitung siklus, mengukur berapa lama suatu operasi tertentu berlangsung, atau mencoba mendeteksi perilaku anomali dengan mengukur variasi waktu yang seharusnya konstan, relatif mudah dilakukan.

Dalam sistem asinkron atau sebagian tanpa jam, referensi waktu yang kaku ini menjadi kabur. Waktu eksekusi suatu operasi dapat bergantung pada ketersediaan data aktual, kemacetan pada jalur internal tertentu, atau variasi fisik kecil. Dari perspektif penyerang, hal ini dapat membuat lebih sulit untuk melancarkan serangan saluran samping berbasis waktukarena jam global yang berfungsi sebagai acuan bersama menghilang.

Namun, sifat dinamis yang sama ini juga mempersulit siapa pun yang ingin mengamati dan mengaudit sistem secara internal. Banyak probe dan penghitung perangkat keras dirancang untuk beroperasi berdasarkan siklus clock; tanpa clock global yang jelas, mengukur kinerja dan mendeteksi aktivitas mencurigakan Kemudian, hal itu membutuhkan metrik dan mekanisme lain.

Selain itu, desain asinkron, dengan terbebas dari pengaruh clock, memungkinkan jalur data diaktifkan pada waktu yang sedikit berbeda di setiap eksekusi, yang berpotensi mengacak kebocoran sementara Namun hal itu juga dapat membuka peluang lain, misalnya dalam bentuk pola konsumsi energi yang berbeda dan lebih kompleks yang dapat dieksploitasi oleh serangan analisis daya.

Representasi data, ukuran kata, dan keamanan

Faktor penting lainnya yang terkait dengan arsitektur CPU adalah bagaimana CPU merepresentasikan dan menangani data. Hampir semua prosesor modern menggunakan representasi biner, dengan nilai tegangan yang sesuai dengan 0 dan 1. Ukuran kata (8, 16, 32, 64 bit…) menentukan rentang bilangan bulat yang dapat ditangani secara langsung dan jumlah memori yang dapat diakses.

Dari sudut pandang keamanan, ukuran kata memengaruhi ruang alamat dan probabilitas tabrakan, luapan, dan kesalahan penunjukSistem 32-bit dengan 2^32 kemungkinan alamat memiliki keterbatasan yang sangat jelas dibandingkan dengan sistem 64-bit. Selain itu, banyak mekanisme proteksi modern, seperti ekstensi memori terlindungi tertentu, bergantung pada ketersediaan ruang alamat yang besar.

Penggunaan MMU dan penerjemahan alamat juga memperkenalkan lapisan tambahan antara program dan memori fisik, sesuatu yang sangat penting untuk proses terisolasiImplementasikan memori virtual dan lindungi kernel. Dalam konteks asinkron, koordinasi antara terjemahan dan sinyal antar blok tanpa jam harus dirancang dengan sangat baik untuk menghindari terciptanya celah keamanan atau kondisi persaingan (race condition).

Selanjutnya, ekstensi vektor (SIMD) dan unit floating-point memungkinkan pengolahan data dalam jumlah besar secara paralel. Ini bagaikan pedang bermata dua: di satu sisi, Ini mempercepat algoritma kriptografi dan tugas analisis.Di sisi lain, jika dieksploitasi secara jahat, ia menyediakan kapasitas komputasi yang besar untuk memecahkan sandi yang lemah atau melancarkan serangan brute-force.

Dalam skenario tanpa jam atau sebagian asinkron, cara unit komputasi paralel ini diprogram dan dilindungi harus mempertimbangkan bahwa Pola pelaksanaan dan konsumsi tidak lagi mengikuti ritme tetap yang ditentukan oleh jam.tetapi akan menanggapi dinamika data yang sebenarnya, yang juga memengaruhi desain tindakan penanggulangan terhadap saluran samping.

Paralelisme masif, multithreading, dan vektor: dampaknya pada keamanan tanpa jam

Prosesor modern bertujuan untuk meningkatkan kinerja tidak hanya dengan menaikkan kecepatan clock, tetapi juga dengan menjalankan lebih banyak pekerjaan secara paralel. Ini melibatkan banyak inti, multithreading perangkat keras, dan Unit vektor yang mampu memproses banyak titik data per instruksi.Ditambah lagi dengan munculnya akselerator khusus seperti GPU, DSP, atau TPU.

Dari perspektif keamanan, setiap blok eksekusi baru dan setiap tingkat paralelisme baru merupakan permukaan tambahan yang perlu dilindungi. Koordinasi sangat diperlukan. konsistensi cache, manajemen memori bersama, mekanisme pengecualian bersama dan menghindari kondisi persaingan dan kebocoran informasi antar thread atau proses konkuren.

Dalam lingkungan tanpa jam atau hibrida, koordinasi ini lebih bergantung pada protokol komunikasi antar blok daripada siklus jam global. Misalnya, sebuah kernel mungkin menggunakan sinyal permintaan dan pengakuan untuk mengakses memori atau sumber daya bersama, dan penundaan efektif akan bergantung pada lalu lintas aktual pada saat itu, bukan pada jumlah siklus tetap.

Perilaku ini, jika dilihat dari luar, membuat serangan tertentu yang bergantung pada pengukuran waktu yang sangat tepat berdasarkan jumlah siklus jam menjadi sulit. Namun pada saat yang sama, perancang keamanan harus melampaui penghitungan siklus dan bergantung pada... penghitung kejadian, pengukuran lalu lintas, konsumsi energi dan tanda-tanda lain untuk mendeteksi perilaku mencurigakan.

Itulah mengapa banyak produsen mengintegrasikan penghitung kinerja perangkat keras, yang memungkinkan pemantauan waktu nyata terhadap hal-hal seperti cache miss, prediksi percabangan yang gagal, akses memori tertentu, dll. Jika digunakan dengan benar, penghitung ini merupakan alat yang ampuh untuk mengoptimalkan kinerja dan... menemukan pola anomali karakteristik dari malware atau eksploitasi tingkat lanjut, bahkan pada arsitektur yang sebagian asinkron.

Virtualisasi, vCPU, dan isolasi di lingkungan modern

Bahan penting lainnya dalam lanskap saat ini adalah virtualisasi. Di cloud, kita terus-menerus bekerja dengan CPU Virtual (vCPU), yang merupakan fragmen logis dari kapasitas pemrosesan yang dialokasikan ke mesin virtual atau kontainer di atas perangkat keras fisik yang digunakan bersama.

Setiap vCPU pada dasarnya adalah sekumpulan thread atau waktu eksekusi yang dijadwalkan oleh hypervisor pada core fisik. Agar hal ini berfungsi dengan baik, CPU fisik menyediakan mode istimewa khusus yang memungkinkan hypervisor untuk membuat dan mengisolasi mesin virtual, mencegat instruksi-instruksi sensitif tertentu dan mengelola memori setiap tamu tanpa mereka dapat saling mengganggu atau memata-matai satu sama lain.

Dalam konteks ini, keamanan tanpa jam (clockless security) menyiratkan bahwa alokasi waktu CPU antar mesin virtual tidak hanya bergantung pada jam yang seragam, tetapi juga pada... mekanisme perencanaan yang lebih dinamis Didukung oleh perangkat keras. Hypervisor masih melihat siklus clock, tetapi bagaimana siklus tersebut diubah menjadi kerja efektif pada setiap inti dapat diubah oleh blok asinkron internal.

Dari sudut pandang keamanan, hal ini menuntut perancangan alat pemantauan yang tidak hanya menghitung tick, tetapi juga dapat menginterpretasikan penghitung kinerja, statistik penggunaan, dan peristiwa tingkat rendah. mendeteksi penyalahgunaan sumber daya, pelarian mesin virtual, atau pola yang tidak biasa. yang menunjukkan adanya intrusi.

Selain itu, dalam lingkungan yang membutuhkan komputasi intensif, di mana unit vektor, GPU, dan akselerator lainnya dimanfaatkan sepenuhnya, pengelola keamanan harus mempertimbangkan bahwa blok-blok ini, baik sinkron maupun asinkron, dapat menjadi alat untuk mempercepat serangan kriptografi, menambang mata uang kripto tanpa sepengetahuan pengguna. atau melakukan analisis terhadap sejumlah besar data yang dicuri.

Performa, konsumsi daya, dan overclocking dibandingkan dengan desain tanpa clock.

Terakhir, kita harus mempertimbangkan hubungan antara kinerja dan konsumsi daya. Meningkatkan frekuensi clock melalui overclocking (misalnya, dengan melakukan Uji stabilitas dengan OCCT) memungkinkan CPU melakukan lebih banyak operasi per detikNamun, hal ini secara signifikan meningkatkan konsumsi daya dan suhu. Bahkan, banyak prosesor saat ini sudah secara dinamis menyesuaikan frekuensi dan tegangan berdasarkan beban kerja dan suhu internal.

Desain asinkron menawarkan alternatif: alih-alih menggunakan jam yang sangat cepat dan mencoba menjaga semuanya tetap sinkron, Mereka membiarkan setiap blok berfungsi sesuai dengan kecepatan yang ditentukan oleh data.Selama periode beban rendah, bagian yang tidak aktif hampir tidak berubah status, sehingga mengurangi konsumsi tanpa memerlukan mekanisme manajemen daya berbasis jam yang kompleks.

Dari perspektif keselamatan, konsumsi yang lebih rendah dan panas yang lebih sedikit bukan hanya masalah lingkungan atau masalah tagihan listrik. Ini juga berarti mengurangi tekanan pada komponen., mengurangi kemungkinan kegagalan yang disebabkan oleh elektromigrasi atau kebocoran arus, dan berpotensi mengurangi paparan terhadap serangan yang mencoba mengeksploitasi perilaku sistem dalam kondisi suhu atau tegangan ekstrem.

Namun, merancang sistem yang sepenuhnya asinkron dan aman bukanlah hal yang mudah. Hal ini membutuhkan verifikasi yang sangat ketat terhadap protokol komunikasi antar blok, kondisi persaingan (race condition), dan keadaan perantara untuk mencegah kesalahan. perilaku non-deterministik yang dapat dieksploitasi oleh penyerangKompleksitas desain, kelangkaan perangkat lunak yang matang, dan kebutuhan akan kompatibilitas mundur dengan perangkat lunak yang ada telah menyebabkan sebagian besar prosesor komersial tetap sinkron dengan beberapa bagian asinkron kecil.

Kombinasi dari semua faktor ini—arsitektur internal, manajemen clock, paralelisme, virtualisasi, dan daya—membuat keamanan di lingkungan tanpa clock global menjadi keseimbangan yang rumit. Desain asinkron mengurangi serangan berbasis timing tertentu dan memfasilitasi strategi penghematan daya yang sangat canggih, tetapi juga menghadirkan tantangan baru untuk pemantauan, audit, dan verifikasi perilaku perangkat keras, sehingga kuncinya terletak pada integrasi. mekanisme pengamatan dan isolasi yang kuat mulai dari silikon itu sendiri hingga perangkat lunak tingkat tertinggi.

Penulis yang bersemangat tentang dunia byte dan teknologi secara umum. Saya suka berbagi ilmu melalui tulisan, dan itulah yang akan saya lakukan di blog ini, menunjukkan kepada Anda semua hal paling menarik tentang gadget, perangkat lunak, perangkat keras, tren teknologi, dan banyak lagi. Tujuan saya adalah membantu Anda menavigasi dunia digital dengan cara yang sederhana dan menghibur.