- Безчасовата сигурност се отнася до асинхронни процесори, където зависимостта от глобален тактов часовник е намалена или елиминирана.

- Съвременните процесори комбинират кеш памети, MMU единици, паралелизъм и множество нишки, което усложнява както производителността, така и сигурността.

- Безчасовите дизайни могат да смекчат атаките, свързани с времето, но изискват нови форми на мониторинг и одит. железария.

- Виртуализацията, vCPU и специализираните ускорители разширяват повърхността за атака, което прави интегрирането на сигурността от нивото на силициевите процесори от съществено значение.

Изразът Безчасовата сигурност звучи като футуристична концепция.Но всъщност това е тясно свързано с начина, по който са проектирани и защитени съвременните процесори и системи. За да го разберем правилно, трябва да се задълбочим в това как работи един процесор вътрешно, как е организирано изпълнението на инструкциите и каква роля играе известният тактов сигнал в задаването на темпото на цялата система.

През последните десетилетия процесорите се надпреварват да увеличат скоростта си. тактова честота, интегриране на повече транзистори и умножаване на паралелизма имВ същото време се появиха дизайни, които се опитват да се освободят от зависимостта от глобалния часовник, било то в целия чип или в определени части. Тази област, тази на асинхронните или безчасови дизайни, открива много интересни възможности по отношение на консумацията на енергия и разсейването на топлината... а също и специфични предизвикателства пред сигурността, които често се групират в рамките на концепцията за безчасова сигурност.

Процесорът като център на системата и връзката му с тактовата честота

Когато говорим за сигурност, свързана с часовници, първото нещо, което трябва да запомним, е какво точно представлява процесорът. По същество, Централният процесор е мозъкът на компютъра.: компонентът, който интерпретира и изпълнява програмни инструкции, координира паметта, входно/изходните операции и специализираните копроцесори, като например графичните процесори (GPU).

В един съвременен процесор откриваме няколко отделни блока. От една страна, това е аритметично-логическо устройство (АЛУ)Аритметично-логическото устройство (АЛУ) е отговорно за математическите и логическите операции с цели числа. След това са регистрите, които са малки, ултрабързи памети, където се съхраняват данните, с които процесорът работи в момента. И на всичкото отгоре има управляващо устройство, което решава, цикъл по цикъл, какво да се прави, какво да се чете от паметта и какво да се записва.

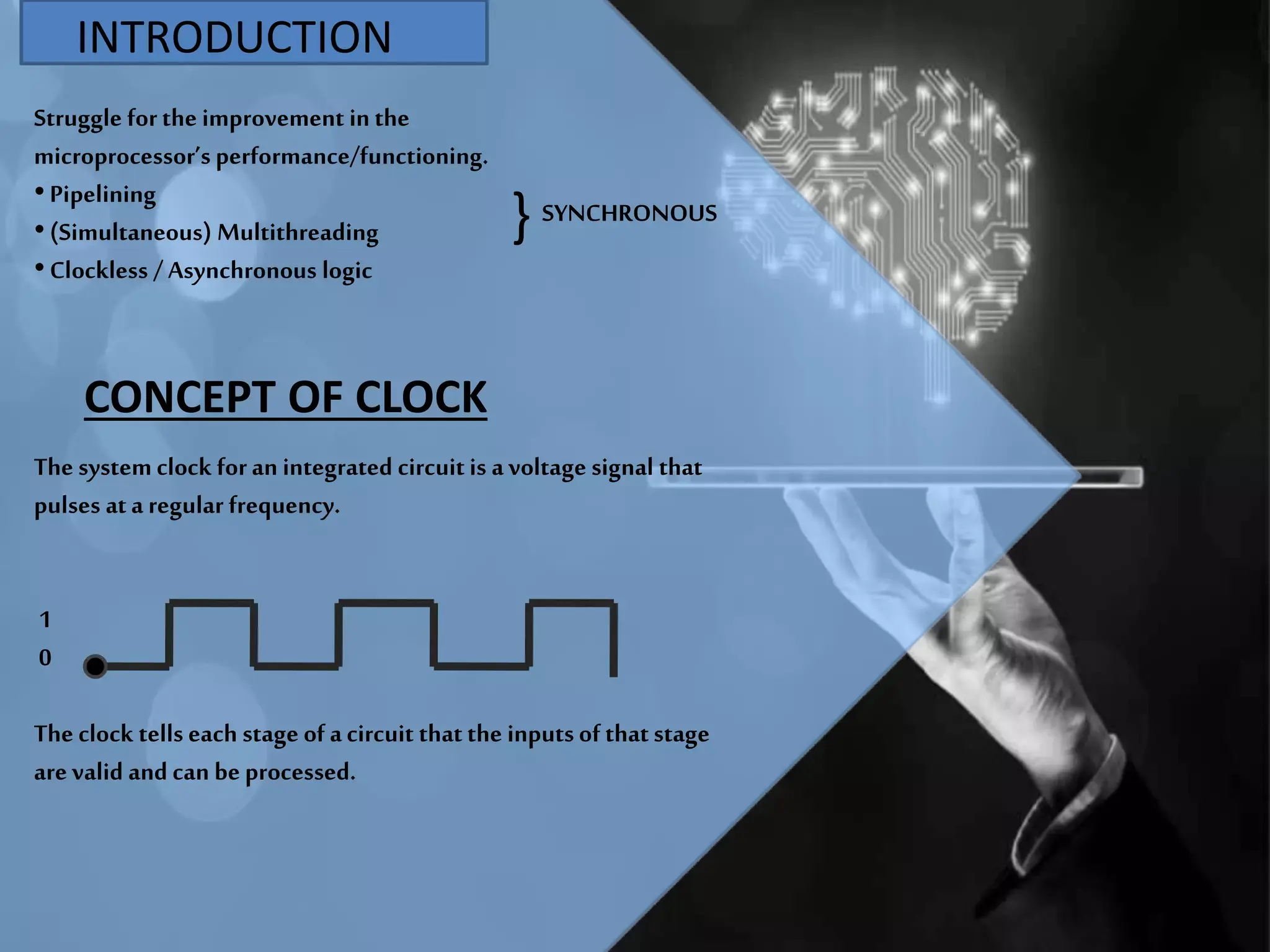

Повечето съвременни процесори са синхронни. Това означава, че всички тези вътрешни блокове са координирани с помощта на периодичен тактов сигналвид електронен метроном, който задава темпото на изпълнение. Всяко тиктакане на този часовник се придвижва с една стъпка от така наречения цикъл на инструкциите: инструкцията се извлича, декодира, изпълнява, резултатите се съхраняват и цикълът започва отново.

В традиционния процесор тактовият генератор се генерира от външен осцилатор, който изпраща милиони или милиарди импулси в секунда. Честотата на тези импулси, измерена в херци, мегахерци или гигахерци, ни казва с колко „такта“ разполага процесорът всяка секунда, за да премества данни и да извършва операции. Колкото по-висока е тактовата честота, толкова повече потенциална работа в секунда.при условие че останалата част от архитектурата я допълва.

По този начин, производителността зависи не само от такта, но и от това колко инструкции на цикъл (IPC) Той е способен да завърши процесора. Продуктът, свързан с честотата и IPC, ни дава представа за милионите инструкции в секунда, които може да изпълнява, въпреки че теоретичните цифри обикновено са много по-оптимистични от това, което всъщност се вижда при реалните програми.

От фиксирано окабеляване до интегрирани микропроцесори

За да поставим безчасовите дизайни в контекст, е полезно да разгледаме как се е развил процесорът. Ранните електронни компютри, като например ENIAC, бяха машини с фиксирана програма с кабелЗа да се променят задачите, системата трябваше да бъде физически пренастроена. Революционната идея беше компютърът със съхранявана програма, в който инструкциите се намират в паметта; процесорът просто ги чете и изпълнява.

Тази архитектура със запаметени програми, свързана с Джон фон Нойман, в крайна сметка надделя. В нея, Инструкциите и данните споделят едно и също пространство в паметтаЗа разлика от архитектурата на Харвард, която физически разделя двата вида информация, днес почти всички процесори с общо предназначение следват архитектура на фон Нойман, въпреки че много чисти или хибридни процесори на Харвард все още съществуват в света на вградените системи.

Първите процесори са били изградени с релета или вакуумни лампи. Те са били обемисти, бавни и са имали... надеждност много ограничен. Преходът към твърдотелни транзистори през 50-те и 60-те години на миналия век позволи радикално увеличаване на скоростта и намаляване на разхода на гориво и размераОттам нататък се премина от дискретни схеми към интегрални схеми (ИС), като все повече транзистори се поставяха върху един чип.

С появата на интегралните схеми, първо малки (SSI), след това средномащабни (MSI), големи (LSI) и накрая много големи (VLSI), процесорът беше компресиран, докато се побере. всичко на един или няколко чипаТази интеграция достигна кулминацията си в микропроцесора, в който целият процесор е произведен на един единствен силициев чип.

El Intel 4004Intel 8080, пуснат на пазара през 1971 г., е един от първите търговски микропроцесори. Скоро след това последвали по-мощни дизайни, като например Intel 8080, който станал основата на персоналните компютри. От този момент нататък терминът „процесор“ почти винаги се използвал за обозначаване на тези микропроцесори.

Ключови вътрешни компоненти на съвременен процесор

Съвременните процесори посвещават огромна част от силициевата си повърхност на помощни елементи, предназначени за... за да извлечете максимума от всеки тактов цикълНапример, почти всеки процесор включва няколко нива на кеш памет: малки, но много бързи памети, разположени близо до ядрата, които съхраняват копия на най-използваните данни, така че да не се налага постоянно да имат достъп до RAM паметта.

В допълнение към кешовете L1, L2 и често L3, един сложен процесор включва и устройство за управление на паметта (MMU) който преобразува виртуалните адреси (тези, обработвани от операционната система) във физически адреси в RAM паметта, управлява виртуална памет и осигурява изолация между процесите.

В изчислителната равнина имаме няколко специализирани изпълнителни устройства: АЛУ за цели числа, единица с плаваща запетая (FPU) За десетични операции се използват единици за генериране на адреси (AGU) за бързо изчисляване на местоположенията в паметта, а в много архитектури се използват векторни единици или SIMD за едновременна работа с множество точки от данни.

Има и управляващ блок, който може да бъде с вградена логика или базиран на микрокод, т.е. вътрешна програма, която превежда всяка инструкция от високо ниво в поредица от вътрешни управляващи сигнали. В много процесори този микрокод може да се актуализира, което позволява коригиране на грешки в дизайна или настройване на поведението след факта.

Накрая, има набор от вътрешни регистри: регистри с общо предназначение, акумулатори, програмни броячи, регистри за състояние с флагове, които показват неща като дали резултатът от дадена операция е нула, отрицателен или е довел до препълване и т.н. Всичко това се координира, следвайки класическия цикъл. заснемане, декодиране и изпълнение на инструкции.

Как да стартирате програма стъпка по стъпка

Основната работа на всеки процесор се свежда до извличане на инструкции от паметта и обработката им една след друга. Това се случва в три основни фази. Първо, етапът на улавяне (донасяне), при която инструкцията, чието адресиране е зададено от програмния брояч, се чете от паметта.

Следва фазата на декодиране. Новозаснетата инструкция преминава през двоичен декодер, който проверява нейния оперативен код (опкод) и преобразува този битов шаблон в конкретни сигнали които активират или деактивират части от процесора. Там се решава дали става въпрос за събиране, преход, зареждане от паметта и т.н., и кои регистри или адреси са включени.

Накрая операцията се изпълнява. ALU или съответното устройство извършва изчислението или преместването на данните и резултатът обикновено се съхранява в регистър или в паметта. Ако е необходимо да се промени програмният поток, например с условен скок, програмният брояч се актуализира с нов адрес. Този набор от инструкции, данни и скокове Именно той формира цикли, функции, условни оператори и цялата логика на нашите програми.

В простите процесори всичко се случва линейно и последователно. Но в съвременните процесори... Много от тези етапи се припокриват, използвайки техники за паралелизъмЦелта е всеки тактов цикъл да извършва възможно най-много работа и хардуерът да не е в режим на празен ход.

Паралелизъм, канализиране и изпълнение извън реда

За да избегнат разхищението на часовника, дизайнерите въведоха... тръбопроводПътят на данните е разделен на няколко етапа, подобно на поточна линия. Докато една инструкция се декодира, следващата вече се извлича от паметта, а друга може да се изпълнява в ALU.

Проблемът е, че понякога една инструкция се нуждае от резултата от друга, която все още не е завършила. Това създава зависимости от данни и налага въвеждането на „балончета“ или чакания в конвейера. За да се минимизират тези забавяния, се използват техники като пренасочване на операнди, предвиждане на разклонения и по-късно, изпълнение извън реда, при който процесорът вътрешно пренарежда инструкциите, стига да се спази крайният резултат от програмата.

Следващата стъпка беше суперскаларен дизайн: оборудване на процесора с няколко изпълнителни устройства от един и същи тип, за да може издава множество инструкции на тактов цикълпри условие че няма конфликти между тях. Вътрешен диспечер анализира потока от инструкции, открива какво може да се изпълни паралелно и ги разпределя между различните устройства.

Всичко това Трикове Те са включени в т.нар. паралелизъм на обучението (ILP)Практическите ограничения на тези техники и нарастващата трудност при по-нататъшно увеличаване на тактовите честоти без значително увеличаване на консумацията на енергия и топлината, доведоха до това, че в определен момент производителите също започнаха да инвестират в... паралелизъм на ниво задачамножество нишки и множество ядра на чип (и механизми като паркинг за ядра).

Ето как се раждат многоядрени процесори и архитектури с хардуерна многонишкова обработка, където всяко ядро може да поддържа състоянието на няколко нишки на изпълнение и бързо да превключва между тях, за да използва по-добре вътрешните ресурси, докато някои нишки чакат данни от паметта.

Ролята на тактовата честота и нейните физически граници

Връщайки се към тактовата честота, важно е да се отбележи, че сигналът, който синхронизира процесора, в крайна сметка е електрически сигнал, който се разпространява през чипаС увеличаване на честотите и нарастване на броя на транзисторите, поддържането на перфектно подравняване на сигнала става много трудно. Възникват проблеми с разпределението на тактовата честота, фазовите измествания и целостта на сигнала.

От друга страна, всеки преход на тактовата честота кара множество транзистори да променят състоянието си, дори ако определена област на процесора не прави нищо полезно в този момент. Това се изразява в консумация на енергия и разсейване на топлина просто за да поддържат метронома работещ. За да се облекчи това, бяха въведени техники като синхронизиране на часовника, което избирателно изключва тактовия сигнал в неизползваните блокове, намалявайки консумацията на енергия.

Въпреки това, след определен праг, увеличаването на честотата престава да бъде разумно: проблемите с консумацията, температурата и разпределението на тактовата честота се увеличават рязко. Това пречка Това е една от причините, поради които е проучена идеята за пълно или частично отказване от глобален часовник: тук влизат в действие асинхронните или „безчасовникови“ дизайни.

В асинхронен дизайн, вместо да има един тактов часовник, който маркира време за целия чип, Самите данни и управляващи сигнали синхронизират операциитеБлоковете комуникират, използвайки протоколи за заявка и потвърждение (ръкостискане): когато данните са готови, производителят уведомява потребителя, а потребителят реагира, без да чака фиксиран фронт на тактовия импулс.

Те са построени напълно асинхронни процесори Съвместим с известни набори от инструкции, като например семейството AMULET, базирано на ARM, или проекти, производни на MIPS. Съществуват и хибридни дизайни, при които само определени устройства (например специфичен ALU) работят без глобален тактов генератор, докато останалата част от процесора остава синхронна.

Какво имаме предвид под „сигурност без часовник“?

Когато говорим за безчасова сигурност, се смесват две идеи: от една страна, асинхронният дизайн като техника за намаляване на потреблението и топлинатаОт друга страна, има значението на това да се премахне необходимостта от часовник при анализа, наблюдението и защитата на поведението на системата срещу атаки или повреди.

В синхронните системи много инструменти за сигурност и мониторинг разчитат на съществуването на стабилен и предвидим темпорален ритъмСравнително лесно е да се броят циклите, да се измери колко време отнема определена операция или да се опита да се открие аномално поведение чрез измерване на вариации във времената, които би трябвало да са постоянни.

В асинхронна или частично безчасова система, тези твърди времеви референции се разреждат. Времето за изпълнение на дадена операция може да зависи от действителната наличност на данни, претоварването на определени вътрешни маршрути или незначителни физически вариации. От гледна точка на нападателя, това може да направи по-трудни за осъществяване атаки по странични канали, базирани на времезащото глобалният часовник, който служи като общ ориентир, изчезва.

Въпреки това, същата тази динамична природа усложнява нещата за всеки, който иска да наблюдава и одитира системата вътрешно. Много сонди и хардуерни броячи са проектирани да работят на базата на тактови цикли; без ясен глобален тактов механизъм, измерване на производителността и откриване на подозрителни дейности След това са необходими други показатели и механизми.

Освен това, асинхронният дизайн, като е освободен от тактовата честота, позволява пътищата за данни да се активират в малко по-различно време при всяко изпълнение, което потенциално... рандомизира временните течове Но това би могло да отвори и други врати, например под формата на различни и по-сложни модели на потребление на енергия, които биха могли да бъдат използвани от атаки за анализ на мощността.

Представяне на данни, размер на думите и сигурност

Друг важен фактор, свързан с архитектурата на процесора, е как той представя и обработва данните. Почти всички съвременни процесори използват двоично представяне, със стойности на напрежението, съответстващи на 0 и 1. Размерът на думата (8, 16, 32, 64 бита…) определя диапазона от цели числа, които могат да бъдат обработвани директно, и количеството адресируема памет.

От гледна точка на сигурността, размерът на думата влияе върху адресното пространство и вероятността за колизии, препълвания и грешки на указатели32-битова система с 2^32 възможни адреса има много ясни ограничения в сравнение с 64-битова система. Освен това, много съвременни механизми за защита, като например някои разширения на защитената памет, разчитат на голямо адресно пространство.

Използването на MMU и преобразуване на адреси също така въвежда допълнителен слой между програмата и физическата памет, нещо от решаващо значение за изолиране на процесиВнедрете виртуална памет и защитете ядрото. В асинхронни контексти, координацията между тези транслации и ръчни сигнали между блоковете без тактов механизъм трябва да бъде много добре проектирана, за да се избегне създаването на пропуски в сигурността или условия на състезание.

От своя страна, векторните разширения (SIMD) и единиците с плаваща запетая позволяват паралелна работа с големи обеми данни. Това е нож с две остриета: от една страна, Ускорява криптографските алгоритми и задачите за анализ.От друга страна, ако бъде използвана злонамерено, тя осигурява голям изчислителен капацитет за разбиване на слаби шифри или за стартиране на атаки с груба сила.

В сценарий без тактова честота или частично асинхронен, начинът, по който тези паралелни изчислителни устройства са програмирани и защитени, трябва да отчита, че Моделите на изпълнение и потребление вече не следват фиксиран ритъм, продиктуван от часовника.но ще реагира на реалната динамика на данните, което също влияе върху проектирането на контрамерки срещу страничните канали.

Масов паралелизъм, многонишковост и вектори: влияние върху сигурността без часовник

Съвременните процесори се стремят да увеличат производителността не само чрез повишаване на тактовата честота, но и чрез паралелно изпълнение на повече работа. Това включва множество ядра, хардуерна многонишкова обработка и... векторни единици, способни да обработват множество точки от данни на инструкцияКъм всичко това се добавя и възходът на специфични ускорители като графични процесори (GPU), цифрови сигнални процесори (DSP) или термични процесори (TPU).

От гледна точка на сигурността, всеки нов блок за изпълнение и всяко ново ниво на паралелизъм е допълнителна повърхност за защита. Координацията е необходима. консистентност на кеша, управление на споделена памет, механизми за взаимно изключване и избягване на условия на състезание и изтичане на информация между нишки или едновременни процеси.

В безчасови или хибридни среди, тази координация разчита повече на комуникационни протоколи между блоковете, отколкото на глобални тактови цикли. Например, ядрото може да използва сигнали за искане и разпознаване за достъп до памет или споделен ресурс, а ефективното забавяне ще зависи от действителния трафик в този момент, а не от фиксиран брой цикли.

Това поведение, погледнато отвън, прави трудни определени атаки, които разчитат на много прецизни измервания на времето, базирани на броя на тактовите цикли. Но в същото време, дизайнерите на сигурност трябва да надхвърлят броенето на цикли и да разчитат на... броячи на събития, измерване на трафика, консумация на енергия и други признаци за откриване на подозрително поведение.

Ето защо много производители интегрират хардуерни броячи на производителността, които позволяват наблюдение в реално време на неща като пропуски в кеша, неуспешни прогнози за клонове, специфични достъпи до паметта и др. Когато се използват правилно, тези броячи са мощен инструмент както за оптимизиране на производителността, така и... намиране на аномални модели характеристика на зловреден софтуер или усъвършенствани експлойти, дори в частично асинхронни архитектури.

Виртуализация, vCPU и изолация в съвременни среди

Друга ключова съставка в днешния пейзаж е виртуализацията. В облака ние постоянно работим с Виртуални процесори (vCPU), които са логически фрагменти от капацитета за обработка, разпределени към виртуални машини или контейнери върху споделен физически хардуер.

Всеки виртуален процесор (vCPU) е по същество набор от нишки или времена за изпълнение, които хипервизорът планира на физическите ядра. За да работи това добре, физическият процесор предлага специални привилегировани режими които позволяват на хипервизорите да създават и изолират виртуални машини, прихващат определени чувствителни инструкции и управляват паметта на всеки гост, без те да могат да се намесват или шпионират един друг.

В този контекст, сигурността без часовник предполага, че разпределението на процесорното време между виртуалните машини зависи не само от еднакъв часовник, но и от по-динамични механизми за планиране поддържано от хардуера. Хипервизорът все още вижда тактови цикли, но начинът, по който тези цикли се преобразуват в ефективна работа на всяко ядро, може да бъде променен от вътрешни асинхронни блокове.

От гледна точка на сигурността, това налага проектирането на инструменти за мониторинг, които не просто броят тактове, но могат също така да интерпретират броячи на производителността, статистика за употреба и събития от ниско ниво. откриване на злоупотреба с ресурси, излизане от виртуална машина или нередовни модели които сочат към проникване.

Освен това, в среди с интензивни изчисления, където векторните модули, графичните процесори и други ускорители се използват пълноценно, мениджърите по сигурността трябва да вземат предвид, че тези блокове, независимо дали са синхронни или асинхронни, могат да се превърнат в инструменти за... ускоряване на крипто атаките, добив на криптовалути зад гърба на потребителя или да извършват анализ на големи обеми от откраднати данни.

Производителност, консумация на енергия и овърклок в сравнение с дизайн без тактова честота

Накрая, трябва да разгледаме връзката между производителността и консумацията на енергия. Увеличаването на тактовата честота чрез овърклок (например чрез извършване на Тест за стабилност с OCCT) позволява на процесор извършва повече операции в секундаТова обаче значително увеличава консумацията на енергия и температурата. Всъщност много съвременни процесори вече динамично регулират честотата и напрежението си въз основа на натоварването и вътрешната температура.

Асинхронните дизайни предлагат алтернатива: вместо да се използва много бърз тактов генератор и да се опитвате да поддържате всичко във фаза, Те позволяват на всеки блок да функционира с темпото, продиктувано от данните.По време на периоди на ниско натоварване, неактивните части почти не променят състоянието си, намалявайки консумацията на енергия, без да са необходими сложни механизми за управление на захранването, базирани на тактова честота.

От гледна точка на безопасността, по-малкото потребление и по-малко топлина не са само екологичен проблем или въпрос на сметки за ток. Това означава също по-малко натоварване на компонентите, по-малка вероятност от повреди, причинени от електромиграция или изтичане на ток, и потенциално по-малко излагане на атаки, които се опитват да експлоатират поведението на системата при екстремни температурни или напреженови условия.

Проектирането на напълно асинхронна и сигурна система обаче не е тривиално. То изисква много строга проверка на комуникационните протоколи между блоковете, условията на състезание и междинните състояния, за да се предотвратят грешки. недетерминистични поведения, които могат да бъдат използвани от нападателСложността на дизайна, недостигът на зрели инструменти и необходимостта от обратна съвместимост със съществуващия софтуер означават, че засега повечето търговски процесори остават предимно синхронни с малки асинхронни острови.

Комбинацията от всички тези фактори – вътрешна архитектура, управление на часовника, паралелизъм, виртуализация и захранване – прави сигурността в среди без глобален часовник деликатен баланс. Асинхронните дизайни смекчават определени атаки, базирани на време, и улесняват високо прецизирани стратегии за пестене на енергия, но те също така представят нови предизвикателства за наблюдение, одит и проверка на поведението на хардуера, така че ключът се крие в интеграцията. надеждни механизми за наблюдаемост и изолация от самия силиций до софтуера от най-високо ниво.

Страстен писател за света на байтовете и технологиите като цяло. Обичам да споделям знанията си чрез писане и това е, което ще направя в този блог, ще ви покажа всички най-интересни неща за джаджи, софтуер, хардуер, технологични тенденции и много други. Моята цел е да ви помогна да се ориентирате в дигиталния свят по лесен и забавен начин.